DesignGateway is Xilinx Alliance Program Certified Partner

#### Features of Classific P COTO series

#### Ultimate IP

High performance, High reliability, Compact resource, Simple user interface

#### Support the Latest Devices

#### Ready to Evaluate on Real FPGA Boards

Able to evaluate IP core performance before purchasing and watch performance demo on Youtube

#### BREFERENCE Design Attached with IP core License Able to start development from the design bit by bit

to shorten time and reliable development

#### Rich Technical Documents

All technical information are available on official website

#### Peoro Security & Configuration

FPGA logic Security System

High-speed FPGA configuration module

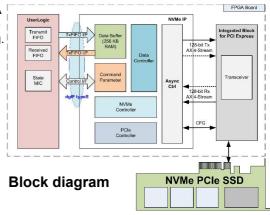

Evaluation on KCU105 with Samsung SSD 960 Pro

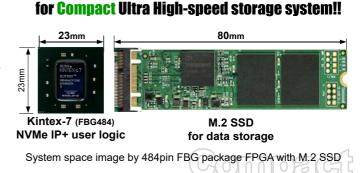

## Directly connect PCIe SSD without external memory!!

**NVMe IP core** interfaces Ultra high-speed PCIe SSD without CPU and external memory. It is the best solution for applications which require ultra high-speed performance with compact system. The IP core license includes the reference design for Xilinx FPGA boards to shorten development time and reduce the cost.

Free evaluation bit files for Xilinx FPGA boards are available. You can evaluate IP core performance before purchasing.

## **Features**

- Implement application layer to access PCIe SSD without CPU and external memory

- Support PCIe Gen3, theoretical upper limit 4GB/sec

- Small resource, the best solution for building a compact system

- FAT32 access without CPU \* with optional FAT32-IP

- Support PLDA PCIe Gen3 Soft IP

- Free evaluation before purchasing

## **Performance,/<u>Application</u>**

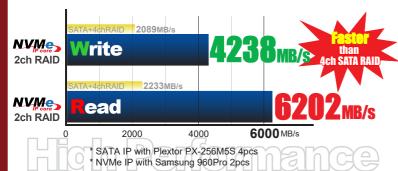

#### Able to build Gen3 PCIe SSD 2ch RAID system!!

## Product,Line.up

#### IP core

| 11 0010                                                                               |                                                              |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------|

| NVMe-IP-VUP                                                                           | 1 project Netlist License for Virtex®UltraScale+             |

| NVMe-IP-ZUP                                                                           | 1 project Netlist License for Zynq <sup>®</sup> UltraScale+  |

| NVMe-IP-KU                                                                            | 1 project Netlist License for Kintex <sup>®</sup> UltraScale |

| NVMe-IP-VT7                                                                           | 1 project Netlist License for Virtex <sup>®</sup> 7          |

| NVMe-IP-KT7                                                                           | 1 project Netlist License for Kintex-7                       |

| NVMe-IP-AT7                                                                           | 1 project Netlist License for Artix <sup>2</sup> 7           |

| NVMe-IP-ZQ7                                                                           | 1 project Netlist License for Zynq <sup>2</sup> 7000         |

| NVMe-IP-FAT32-X                                                                       | FAT32 file system for NVMe-IP. Purchase with NVMe-IP core    |

| Please ask us about Multi-License, Evaluation License and Maintenance support License |                                                              |

#### Reference Designs are available for practical applications

## Easy to apply for high-end products such as ultra high-speed data recorder

Suitable for high-speed data recording and stand-alone data analysis on SoC

The best solution

#### Accessories for evaluation

IP core Evaluation Demo are available on youtube

#### Design Gateway Co.,Ltd.

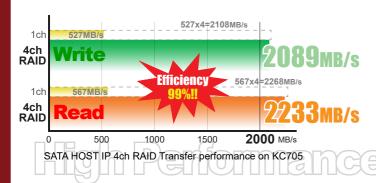

RAID evaluation on KC705 with 4 SSDs

## high-reliability & high-performance IP core proven by NASAH

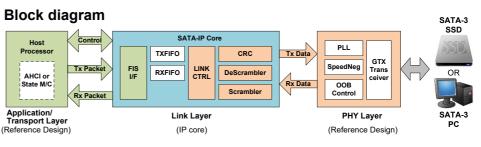

**SATA IP core** compliant with the Serial ATA specification revision 3.0 and works on Xilinx UltraScale, 7-Series, Virtex5/6 and Spartan-6 device. This IP core provides link layer. Design Gateway provide transport layer and 150MHz GTX physical layer design for 6.0Gbps SATA3 interface as reference design. It can connect with SATA3 SSD/HDD directly without external PHY chip. The IP core license includes the reference design for Xilinx FPGA boards to shorten development time and reduce the cost.

## **Features**

- Compliant with SATA 3.0 6Gbps

- Support both Host and Device

- AHCI for Linux boot up from Zynq-7000

- FAT32 access without CPU

\* with optional HCTL-IP and FAT32-IP

- Free evaluation before purchasing IP core Evaluation Demo are available on youtube

- Reference Design is contained with IP core license

## Suitable,for,RAID,System

#### High-Efficiency Loss less RAID system !!

#### Enhanced development support

#### △1 Slice LUTs (218600) Slice Registers (437200) Slice (54650) 2426 u\_AllIdenRam[0].u\_IdenRam (Ram128x32) u\_AllIdenRam[1].u\_IdenRam (Ram128x32\_HD172 u\_AllIdenRam[2].u\_IdenRam (Ram128x32\_HD179) u AllIdenRam[3].u IdenRam (Ram128x32 HD186) u\_CpuLAxi2Reg (LA u\_IP2UFf (FIF0512) 116 209 195 5: I U SATARAIDOx4IP (SAT 6769 2839 B () U\_HSATAIPO (HSATAIPMI) B () U\_HSATAIP1\_3[1].U\_HSATAIP1 (HSATAIPSI) B () U\_HSATAIP1\_3[2].U\_HSATAIP1 (HSATAIPSI\_0) B () U\_HSATAIP1\_3[3].U\_HSATAIP1 (HSATAIPSI\_1) 1551 1581 10 658 155 657 675 1581 1552 1586 13 **CALC 4ch RAID Total Resouce Usage**

Able to build RAID system by Small Resource !!

#### Resource consumption of SATA IP+HCTL IP 4ch RAID reference design for KC705

## Product,Line.up

| IP core         |                                                             |

|-----------------|-------------------------------------------------------------|

| SATA-IP-KU      | 1 project Netlist License for Kintex UltraScale             |

| SATA-IP-ZUP     | 1 project Netlist License for Zynq <sup>®</sup> UltraScale+ |

| SATA-IP-KT7     | 1 project Netlist License for Kintex <sup>®</sup> 7         |

| SATA-IP-ZQ7     | 1 project Netlist License for <b>Zynq<sup>©</sup>-7000</b>  |

| SATA-IP-AT7     | 1 project Netlist License for Artix <sup>2</sup> 7          |

| SATA-IP-VT7     | 1 project Netlist License for Virtex <sup>®</sup> -7        |

| SATA-IP-HCTL-X  | HOST IP for SATA-IP. Purchase with SATA-IP core             |

| SATA-IP-AHCI-A  | AHCI function for LinuxOS. Purchase with SATA-IP core       |

| SATA-IP-FAT32-X | FAT32 file system for SATA-IP. Purchase with SATA-IP core   |

| SATA-IP-exFAT-X | exFAT file system for SATA-IP. Purchase with SATA- IP core  |

#### Accessories for evaluation

| AB02-CROSSOVER | SATA- SATA crossover board<br>for SATA Device IP evaluation                              |  |

|----------------|------------------------------------------------------------------------------------------|--|

| AB09-FMCRAID   | FMC-SATA(10ch) adapter board<br>for SATA-IP with RAID evaluation<br>*Available on Mouser |  |

| AB14-CLKSMA    | SMA clock module for AC701                                                               |  |

SATA-IP core for Virtex-5, Virtex-6and Spartan-6 are also available.

Please ask us about Multi-License, Evaluation License and Maintenance support License. For more detail and technical information on our web site http://www.dgway.com/SATA-IP\_X\_E.html

#### Design Gateway Co.,Ltd.

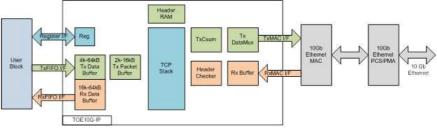

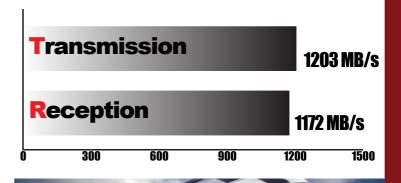

## **10CbE TCP/IP Stack Implementation** by All HW Logic without CPU

10GbE TCP Off-loading Engine(TOE10G-IP) IP core is the epochal solution implemented without CPU. Generally, TCP processing is so complicated that expensive high-end CPU is required. TOE10G-IP built by pure hardwired logic can take place of such extra CPU for TCP protocol management. This IP product includes reference design which helps you to reduce development time. DesignGateway provide demo binary file for Xilinx FPGA boards. You can evaluate TOE10G-IP core on real board before purchasing.

TCP Offloading Engine IP Core

Real time uncompressed HD image transmission

#### **Features**

- Over 1200MByte/sec real transfer speed

- Support Full Duplex

- Fully hard-wired TCP/IP protocol control to build CPU-less network system

- Support Multi-Session

- Free evaluation before purchasing

### for 1Gbit Ethernet

## **Product**,Line.up

#### TOE10G-IP core

| TOE10G-IP-ZUP | 1 project Netlist License for <b>Zynq<sup>®</sup>Ultrascale+</b> |

|---------------|------------------------------------------------------------------|

| TOE10G-IP-KU  | 1 project Netlist License for Kintex®Ultrascale                  |

| TOE10G-IP-ZQ7 | 1 project Netlist License for <b>Zynq<sup>©</sup>7000</b>        |

| TOE10G-IP-KT7 | 1 project Netlist License for Kintex <sup>®</sup> 7              |

| TOE10G-IP-VT7 | 1 project Netlist License for Virtex <sup>®</sup> 7              |

1Gbit TCP Off-loading All Hardware Logic

NITHOUT CPU

For more detail and technical information on our web site www.dgway.com/TOE10G-IP X E.html Please ask us about Multi-License, Evaluation License and Maintenance support License

#### TOE1G-IP core

| TOE1G-IP-ZQ7                                                                              | 1 project Netlist License for <b>Zynq<sup>®</sup>7000</b>  |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------|

| TOE1G-IP-AT7                                                                              | 1 project Netlist License for Artix <sup>®</sup> 7         |

| TOE1G-IP-KT7                                                                              | 1 project Netlist License for <b>Kintex</b> <sup>®</sup> 7 |

| TOE1G-IP-VT7                                                                              | 1 project Netlist License for Virtex <sup>©</sup> 7        |

| TOE1G-IP-SP6                                                                              | 1 project Netlist License for <b>Spartan<sup>®</sup>6</b>  |

| For more detail and technical information on our web site www.dgway.com/TOE1G-IP_X_E.html |                                                            |

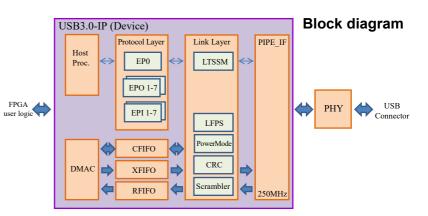

# **Block diagram**

### **Performance**

Ideal for network applications that require broadcast and low latency!!

- All hardware logic to achive CPU-less system

- Minimum overhead and very low latency

- Support Full Duplex

- Free evaluation before purchasing

For more detail and technical information on our web site www.dgway.com/UDP10G-IP\_X\_E.html and www.dgway.com/UDP-IP\_X\_E.html

Designgateway IP core IP core Evaluation Demo are available on youtube

#### Design Gateway Co.,Ltd.

# http://www.dgway.com/IPcores\_A\_E.html

## Easy to apply to FAT32 Data Recorder System!

**USB3.0 IP core** complaints with the USB 3.0 specification Revision1.0. This IP core provides link layer and protocol layer. Physical layer interfaces to PHY chip by TI. Mass storage class reference design for Xilinx<sup>®</sup> FPGA board is included in the IP core license. You can start your development from the design step by step and shorten development time and reduce the cost.

USB3.0-IP Evaluation on SP605 with AB07-USB3FMC

#### **Features**

Line up both Host & Device

Ready to start Dev. on real board!! Provide reference design for Xilinx<sup>®</sup> FPGA boards

Host IP

FAT32 File access demo

Informe Designs for practice applications

Device IP

FAT32 Data recording demo

Complaint with USB 3.0 5Gbps

Support All transmission taps

## Reference,Designs,are,available,for,practical,applications,

FPGA records data and transfers it through USB3.0. At PC side, it is recognized as FAT32 files.

At PC side, it is recc roduct line un

Product,Line.up

| IP core      |                                                                 |

|--------------|-----------------------------------------------------------------|

| USB3D-IP-SP6 | Host IP. 1 project Netlist License for Spartan <sup>®</sup> 6   |

| USB3D-IP-VT6 | Host IP. 1 project Netlist License for Virtex <sup>®</sup> 6    |

| USB3D-IP-KT7 | Host IP. 1 project Netlist License for Kintex <sup>®</sup> 7    |

| USB3D-IP-VT7 | Host IP. 1 project Netlist License for Virtex <sup>®</sup> 7    |

| USB3D-IP-ZQ7 | Host IP. 1 project Netlist License for Zynq <sup>®</sup> 7000   |

| USB3H-IP-SP6 | Device IP. 1 project Netlist License for Spartan <sup>®</sup> 6 |

| USB3H-IP-VT6 | Device IP. 1 project Netlist License for Virtex <sup>®</sup> 6  |

| USB3D-IP-KT7 | Device IP. 1 project Netlist License for Kintex <sup>2</sup> 7  |

| USB3H-IP-VT7 | Device IP. 1 project Netlist License for Virtex <sup>®</sup> 7  |

| USB3H-IP-ZQ7 | Device IP. 1 project Netlist License for Zynq <sup>®</sup> 7000 |

#### Accessories for evaluation

FMC-USB3.0 adaptor board USB3.0 TypeA to A cable (1m) is contained "-1.8VIF" : FMC I/O voltage is 1.8V only.

検索 IIm

Please ask us about Multi-License, Evaluation License and Maintenance support License. For more detail and technical information on our web site www.dgway.com/USB3-IP\_X\_E.html

You Tube Designgateway IP core

IP core Evaluation Demo are available on youtube

## Adapter Boards For IP Core Evaluation

**AB Series** is Extension Adapter Boards for Gigabit IP core evaluation. AB Series support Xilinx FPGA boards. By using AB Series, Gigabit IP cores work on Xilinx FPGA boards.

## For Evaluation before Purchasing

M.2-FMC adapter board for NVMe-IP evaluation. Able to connect 2 NVMe SSDs. \* SSD is not included.

For more detail and technical information on our web site http://www.dgway.com/ABseries\_E.html

AB17-M2FMC

VC707, VC709 ZCU102 and

FMC I/F mounted

Xilinx FPGA boards

IVMe-

# **IPLOCK** Protect Intellectual Property from Illegal copy

IPLock is FPGA logic security system which used very reliable AES encryption technology. IP properties in FPGA are protected from illegal copy by only including IP Lock in FPGA and connecting with encryption controller chip.

#### **Features**

- Strong security by AES-128 encryption

- Change & encrypt true random authentication data

- Immediately stop user logic without the chip

- Just 2 line connection between FPGA and IP Lock

- Laboratories Pack for prototype, already written unique ID

- Writer Set & Blank Encryption chip for mass production

#### <u>Laboratories,Pack,for,prototype</u>

Contents of Laboratories pack. Encryption chips unique ID inside Laboratories Pack contains encryption chips which are already written unique ID at shipment by Design Gateway. No one can rewrite this fixed ID key. To avoid duplication, each Laboratories pack have different unique ID key, so user must use IP Lock core with encryption chips in same package. Design Gateway provide encryption chip 10 pcs package (IPL-010L) and 30 pcs package (IPL-030L). This product is suitable for prototype and small lot usage.

IPL-010L IP core netlist + encryption controller chip (unique ID inside) 10pcs pack IPL-030L IP core netlist + encryption controller chip (unique ID inside) 30pcs pack

Writer pack is suitable for mass production. User can write any ID key to blank encryption chip by using IP Lock write. User can set and write optional ID key for each products or lot. Writer pack contains blank chip 3 pcs. For mass production, The Writer pack is used with Blank Chip

Designgateway IPlock

IPLock Demo is available on youtube

檢和

IPLock Writer and IPL-CHP

IPL-003WR IPLock Writer, IPLick core + IPL-CHP 3pcs (Blank Encryption chip) IPL-CHP Blank Encryption chip for IPL-003WR (MOQ 100pcs)

Easy to protect vour IP core & logic data !

Place IPLock security chip

on your FPGA board

FPGA

Step1: Prepare SOIC-8 pattern for security chip on your board Step2: purchase IPLock for FPGA logic protection Step3: Compile your FPGA logic with IPLock core t IPLock security c ip Step5: Protected!! Complete P core protection

**Purchasing available on Mouser**

You lube

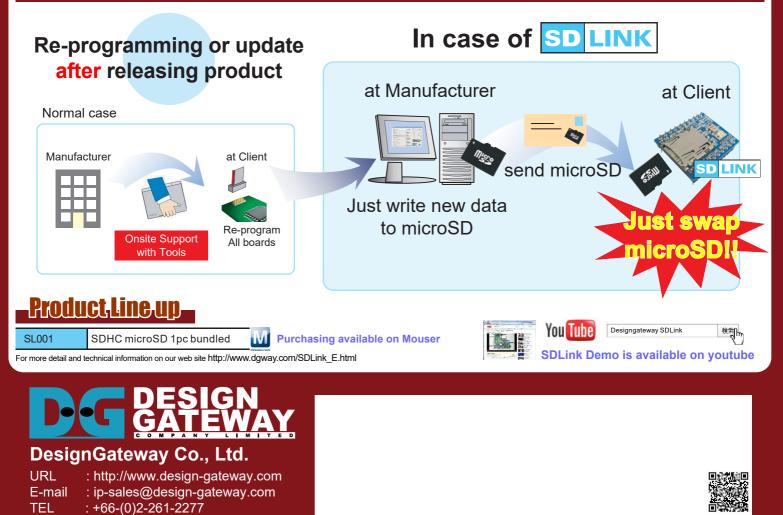

## Convenient and High-Speed Configuration Module via microSD

#### Ultra High-Speed Programming!!

Just 3 second to program 20MBytes (=160Mbit) configuration data. (comparison with on board flash, it takes about 7 minutes...)

to update & change circuit data immediately!!

Convenient update without Programming tools, Download cable

## Only one SDLink can configure up to 8 FPGAs at same time.

Just swap microSD

and System suspended.

**SDLink** is a high speed FPGA configuration module which stores data on microSD card. FPGA configuration data is easily updated by just swapping microSD card.

# High-Speed Configuration Convenient field update Tool free High-Speed Programming Easy to swap

## **Practical example**