# TOE10GLL-IP (Cut-through) 32-session reference design

| 1 | Intro | oduction                                      | 1  |

|---|-------|-----------------------------------------------|----|

| 2 | Har   | dware overview                                | 2  |

|   | 2.1   | Xilinx Transceiver (PMA for 10GBASE-R)        | 3  |

|   | 2.2   | LL10GEMAC                                     | 3  |

|   | 2.3   | PMARstCtrl                                    |    |

|   | 2.4   | TOE10GLL                                      | 3  |

|   | 2.5   | TxEMACMux8to1 and TxEMACMux4to1               | 4  |

|   | 2.5   | .1 TxEMACMux8to1                              | 4  |

|   | 2.5   | .2 TxEMACMux4to1                              | 5  |

|   | 2.6   | CPU and Peripherals                           | 6  |

|   | 2.6   | .1 AsyncAxiReg                                | 7  |

|   | 2.6   | .2 UserReg                                    | 9  |

| 3 | CP    | U Firmware (FPGA)                             | 12 |

|   | 3.1   | Display parameters                            |    |

|   | 3.2   | Reset parameters                              | 16 |

|   | 3.3   | Half Duplex Test                              |    |

|   | 3.4   | Full duplex test                              | 19 |

|   | 3.5   | Function list in User application             | 21 |

| 4 | Tes   | st Software on PC                             | 24 |

|   | 4.1   | "tcpdatatest" for half duplex test            | 24 |

|   | 4.2   | "tcp_client_txrx_single" for full duplex test | 26 |

| 5 | Re    | vision History                                | 28 |

## TOE10GLL-IP (Cut-through) 32-session reference design

Rev1.0 3-Jul-23

#### 1 Introduction

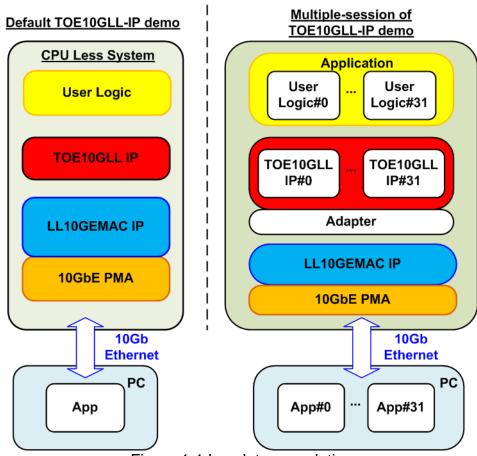

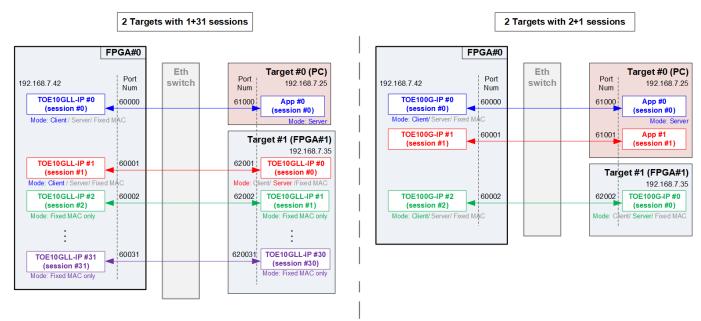

The default TOE10GLL-IP reference design implements one TOE10GLL-IP for transferring TCP payload data by using one session. For some applications such as FINTECH, it always uses more than one session for transfer many data types at the same time. To support multi-session feature with the lowest latency time, many TOE10GLL-IPs configured in Cut-through mode are applied but shares the same Ethernet MAC via adapter.

Figure 1-1 Low-latency solution

This document describes the reference design that includes thirty-two TOE10GLL-IPs that share the same 10GEMAC and PHY to support thirty-two sessions. User logic and Test application for running multiple-session demo are almost similar to one-session demo, except the test application of full-duplex demo. "tcp\_client\_txrx\_single" is applied to run on PC instead. This application is run the test for one round, not forever loop like "tcp\_client\_txrx".

Though the multiple-session demo implements thirty-two sessions, the user can enable each TOE10GLL-IP independently to check the performance or the operation when using less than thirty-two sessions. Also, the transfer direction of each session can be configured independently. The user can modify the multiple-session reference design to adjust the number of sessions to match the system requirement. More details of the demo are described as follows.

#### 2 Hardware overview

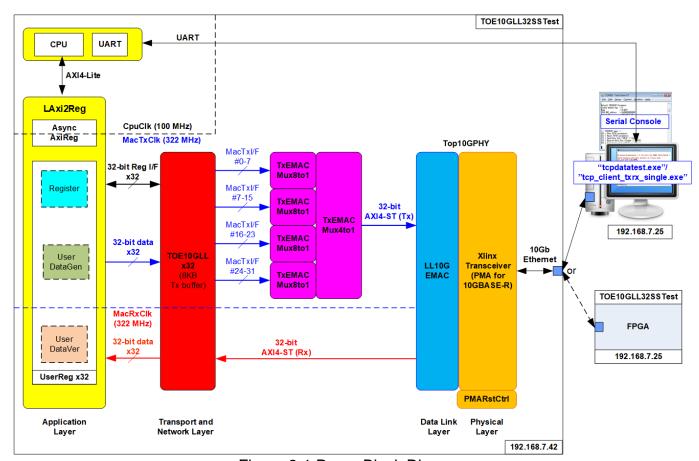

Figure 2-1 Demo Block Diagram

The test system includes CPU for the ease of user interface and flexibility of test environment. User can input the test parameters such as network parameters and transfer size. Also, the current status of the test system such as current transfer size is displayed on Serial console for monitoring the test progress. To connect the hardware with CPU system, AXI4-Lite bus must be implemented. LAxi2Reg is the interface module to convert AXI4-Lite interface to be the user interface of TOE10GLL-IP module. LAxi2Reg includes AsyncAxiReg which is designed to be asynchronous module between CpuClk which is the independent clock for running the CPU system and MacTxClk which is the clock output, generated by Xilinx transceiver module.

The thirty-two TOE10GLL-IPs is applied for running up to 32 sessions with one or many connect target devices. TOE10GLL-IP is configured to Cut-through mode to achieve the lowest latency time and integrates 8 KB Tx buffer to reduce total amount of buffer size in the system. Therefore, test performance may be reduced from one session demo. Each TOE10GLL-IP connects to each UserReg within LAxi2Reg module to control and monitor the TOE10GLL-IP. UserReg consists of UserDataGen module which is the 32-bit test data generator and UserDataVer module which verifies the data, extracted from received packet. Register files inside UserReg are written and read by CPU firmware through AXI4-Lite bus. Another side of thirty-two TOE10GLL-IPs which have thirty-two MacTxI/F are connected to 10G Ethernet MAC controller (LL10GEMAC-IP) via four TxEMACMux8to1 modules and one TxEMACMux4to1 module. While Rx interface of 10G Ethernet MAC controller is fed to thirty-two TOE10GLL-IPs directly. LL10GEMAC-IP implements the Ethernet MAC layer and PCS layer with less latency time. Tx and Rx interface of AXI4-ST are run in the different clock domains: MacTxClk and MacRxClk respectively.

dg\_toe10gllip\_32ss\_refdesign\_xilinx\_en.doc

LL10GEMAC-IP provided by Design Gateway requires to run with Xilinx Transceiver which is configured to be PMA module for 10GBASE-R interface. PMARstCtrl is designed to control the reset sequence of Xilinx Transceiver

Another side of 10Gb Ethernet is the target device, Test PC or another FPGA board. When using TestPC, the test application (tcpdatatest and tcp\_client\_txrx\_single) must be run for transferring TCP data with TOE10GLL-IP. Otherwise, another FPGA board is applied by implementing multiple TOE10GLL-IPs to transfer data in the different direction to show better performance.

#### 2.1 Xilinx Transceiver (PMA for 10GBASE-R)

PMA IP core for 10Gb Ethernet (BASE-R) can be generated by using Vivado IP catalog. In FPGA Transceivers Wizard, the user uses the following settings.

• Transceiver configuration preset: GT-10GBASE-R

Encoding/Decoding : Raw

Transmitter Buffer : Bypass

Receiver Buffer : Bypass

User/Internal data width : 32

The example of Transceiver wizard in Ultrascale model is described in the following link. https://www.xilinx.com/products/intellectual-property/ultrascale\_transceivers\_wizard.html

#### 2.2 LL10GEMAC

The IP core by Design Gateway implements low-latency EMAC and PCS logic for 10Gb Ethernet (BASE-R) standard. The user interface is 32-bit AXI4-stream bus. Please see more details from LL10GEMAC datasheet on our website.

https://dgway.com/products/IP/Lowlatency-IP/dg\_II10gemacip\_data\_sheet\_xilinx\_en.pdf

#### 2.3 PMARstCtrl

When the buffer inside Xilinx Transceiver is bypassed, the user logic must control reset signal of Tx and Rx buffer. The module is designed by state machine to run following step.

- (1) Assert Tx reset of the transceiver to '1' for one cycle.

- (2) Wait until Tx reset done, output from the transceiver, is asserted to '1'.

- (3) Finish Tx reset sequence and de-assert Tx reset to allow the user logic beginning Tx operation.

- (4) Assert Rx reset to the transceiver.

- (5) Wait until Rx reset done is asserted to '1'.

- (6) Finish Rx reset sequence and de-assert Rx reset to allow the user logic beginning Rx operation.

#### 2.4 TOE10GLL

TOE10GLL-IP is the IP core provided by Design Gateway to implement the TCP/IP stack and offload engine for the low latency solution. User interface has two signal groups, i.e., control signals and data signals. The IP can be configured to run in two modes: Cut-through mode and Simple mode. Also, Tx buffer can be configured to balance resource utilization and test performance. TOE10GLL-IP in this reference design is configured to Cut-through mode and 8 KB Tx buffer. More details are described in datasheet.

https://dgway.com/products/IP/Lowlatency-IP/dg\_toe10gllip\_data\_sheet\_xilinx\_en.pdf

#### 2.5 TxEMACMux8to1 and TxEMACMux4to1

The system consists of thirty-two TOE10GLL-IPs which share the same EMAC. To meet timing constraint in some FPGA models, two multiplexer modules are designed, i.e., TxEMACMux8to1 and TxEMACMux4to1. To transfer the transmitted packet from thirty-two TOE10GLL-IPs to one EMAC, four TxEMACMux8to1s are applied to connect with TOE10GLL-IP#0-7, #8-15, #16-23, and #24-31. Then, the transmitted packet output from four TxEMACMux8to1s are fed to one TxEMACMux4to1 for transferring with EMAC. By using two-step multiplexers, the latency time is increased by 2 clock cycles, comparing to using one TOE10GLL-IPs and one MEAC. If the system consists eight or less than eight TOE10GLL-IPs, it can use one-step multiplexer to reduce latency time. More details about TxEMACMux8to1 and TxEMACMux4to1 are described as follows.

#### 2.5.1 TxEMACMux8to1

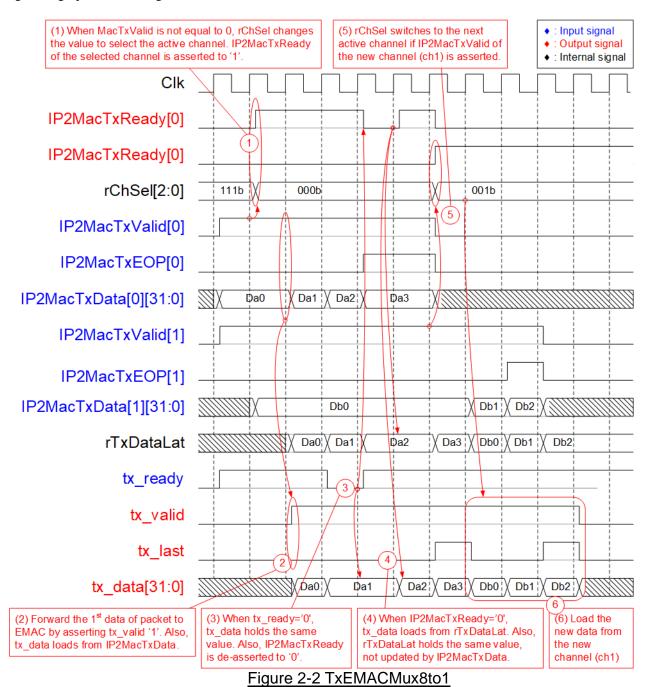

The core signal inside those modules is rChSel that is applied to select one active TOE10GLL-IPs module from eight modules. Timing diagram of this module is displayed in Figure 2-2.

- 1) If current channel (Ch#7) does not transfer the data and the new channel requests to transfer data by asserting IP2MacTxValid to '1', rChSel (the signal to indicate the active channel) will switch the value to the new channel. In Figure 2-2, there are two channels send the request at the same time. The selected channel will be the nearest channel of the order 0 -> 1 -> 2 ->...->7 -> 0. Therefore, Ch#0 is higher priority than Ch#1 when the current channel is 7. IP2MacTxReady of the selected channel (Ch#0) is asserted to '1' to accept the first data.

- 2) The input signals of the selected channel (Ch#0), i.e., IP2MacTxEOP (end-of-packet) and IP2MacTxData (32-bit data) are loaded to the output signals of EMAC (tx\_last and tx\_data respectively). Also, tx\_valid is asserted to '1' to start sending the new packet to EMAC.

- 3) When EMAC is not ready to receive data by de-asserting tx\_ready to '0', all output signals of EMAC hold the same value. Also, IP2MacTxReady of the active channel is de-asserted to '0' to hold the input signals from the source.

- 4) After EMAC re-asserts tx\_ready to accept the data, the next output signals to EMAC will be loaded from the internal latch register (rTxDataLat). The internal latch register is designed to load the data from the active source when IP2MacTxReady is asserted to '1'. Therefore, the latch register is the temp buffer for storing the unsent data to EMAC when EMAC pauses data transmission.

- 5) After accepting the final data of a packet from the active channel, the next active channel is scanned. If IP2MacTxValid of remaining channels is asserted, rChSel will update the value following the rule (0 -> 1 -> 2 ->...-> 7 ->0). In Figure 2-2, the next active channel is Ch#1, so rChSel is set to 001b to accept the data from Ch#1.

- 6) The input signals (IP2MacTxEOP, and IP2MacTxData) of the active channel (Ch#1) are forwarded to be the output signals of EMAC (tx\_last, and tx\_data) until the final data of the packet is transferred.

#### 2.5.2 TxEMACMux4to1

The logic inside TxEMACMux4to1 is almost similar to TxEMACMux8to1, but rChSel is updated to two-bit signal to select Ch#0 – Ch#3. The channel order in this module is 0 -> 1 -> 2 -> 3 -> 0.

#### 2.6 CPU and Peripherals

32-bit AXI4-Lite is applied to be the bus interface for the CPU accessing the peripherals such as Timer and UART. To control and monitor the test system, the control and status signals are connected to register for CPU access as a peripheral through 32-bit AXI4-Lite bus. CPU assigns the different base address and the address range to each peripheral for accessing one peripheral at a time.

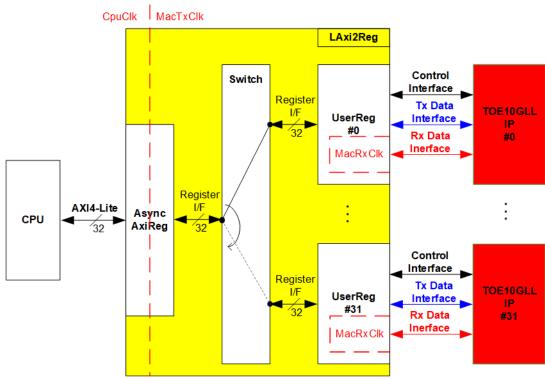

In the reference design, the CPU system is built with one additional peripheral to access the test logic. Therefore, the hardware logic must be designed to support AXI4-Lite bus standard for CPU write access and read access. LAxi2Reg module is designed to connect the CPU system as shown in Figure 2-3.

Figure 2-3 LAxi2Reg block diagram

Similar to the default TOE10GLL-IP reference design, LAxi2Reg consists of AsyncAxiReg and UserReg. To support multiple sessions, thirty-two UserRegs are integrated. Therefore, switch logic is designed to decode the requested address by AsyncAxiReg. Five upper bits are applied for selecting the active channel from 32 channels (00000b-UserReg#0, 00001b-UserReg#1, ..., 11111b-UserReg#31).

AsyncAxiReg and UserReg are the same module applied in the default TOE10GLL-IP reference design. AsyncAxiReg converts the AXI4-Lite signals to be the simple register and includes asynchronous logic to support clock domain crossing between CpuClk domain and MacTxClk domain. UserReg is the example of user logic to interface with TOE10GLL-IP. Tx data interface and Rx data interface of TOE10GLL-IP are run in different clock domain, MacTxClk and MacRxClk. Therefore, UserReg module consists of the logics which run in two clock domains. More details of AsyncAxiReg and UserReg are described as follows

#### 2.6.1 AsyncAxiReg

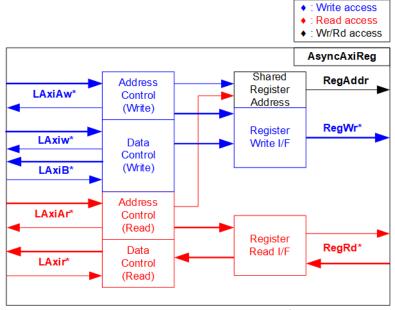

Figure 2-4 AsyncAxiReg Interface

The signal on AXI4-Lite bus interface can be split into five groups, i.e., LAxiAw\* (Write address channel), LAxiw\* (Write data channel), LAxiB\* (Write response channel), LAxiAr\* (Read address channel) and LAxir\* (Read data channel). More details to build custom logic for AXI4-Lite bus are described in following document.

https://forums.xilinx.com/xlnx/attachments/xlnx/NewUser/34911/1/designing\_a\_custom\_axi\_slave\_rev1.pdf

According to AXI4-Lite standard, the write channel and the read channel are operated independently. Also, the control and data interface of each channel are run separately. So, the logic inside AsyncAxiReg to interface with AXI4-Lite bus is split into four groups, i.e., Write control logic, Write data logic, Read control logic, and Read data logic as shown in the left side of Figure 2-4. Write control I/F and Write data I/F of AXI4-Lite bus are latched and transferred to be Write register interface with clock domain crossing registers. Similarly, Read control I/F of AXI4-Lite bus are latched and transferred to be Read register interface. While the returned data from Register Read I/F is transferred to AXI4-Lite bus by using clock domain crossing registers. In register interface, RegAddr is shared signal for write and read access. Therefore, it loads the address from LAxiAw for write access or LAxiAr for read access.

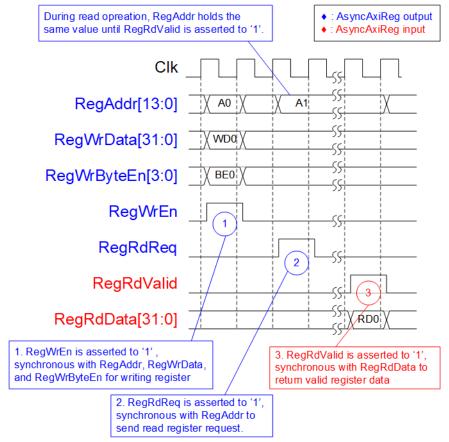

The simple register interface is compatible with single-port RAM interface for write transaction. The read transaction of the register interface is slightly modified from RAM interface by adding RdReq and RdValid signals for controlling read latency time. The address of register interface is shared for write and read transaction, so user cannot write and read the register at the same time. The timing diagram of the register interface is shown in Figure 2-5.

Figure 2-5 Register interface timing diagram

- 1) To write register, the timing diagram is similar to single-port RAM interface. RegWrEn is asserted to '1' with the valid signal of RegAddr (Register address in 32-bit unit), RegWrData (write data of the register), and RegWrByteEn (the write byte enable). Byte enable has four bits to enable 4-byte data. Bit[0], [1], [2], and [3] are equal to '1' when RegWrData[7:0], [15:8], [23:16], and [31:24] are valid respectively.

- 2) To read register, AsyncAxiReg asserts RegRdReq to '1' with the valid value of RegAddr. 32-bit data is returned after receiving the read request. The slave detects RegRdReq asserted to start the read transaction. During read operation, the address value (RegAddr) does not change until RegRdValid is asserted to '1'. Therefore, the address can be used for selecting the returned data by using multiple levels of multiplexer.

- 3) The read data is returned on RegRdData bus by the slave with asserting RegRdValid to '1'. After that, AsyncAxiReg forwards the read value to LAxir\* interface.

#### 2.6.2 UserReg

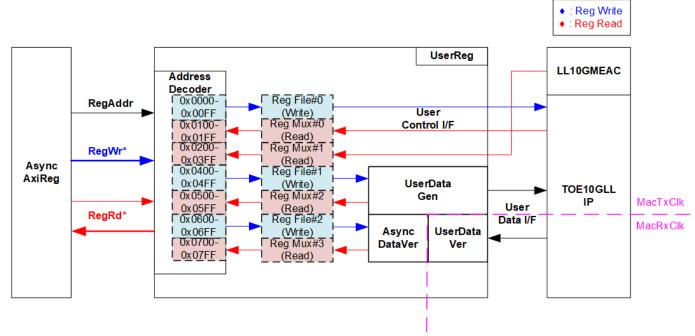

Figure 2-6 UserReg block diagram

UserReg module applied in 32-session demo is similar to 1-session demo, so please see more details about the hardware logic and the operation from 1-session demo document. https://dgway.com/products/IP/Lowlatency-IP/dg\_toe10gllip\_refdesign\_xilinx\_en.pdf

As shown in Figure 2-6, register map of one session uses 800h address area (0x0000 – 0x07FF), so 32-session is implemented by mapping to 10000h area as below.

- 0x0000 0x07FF: Session#0 hardware

- 0x0800 0x0FFF: Session#1 hardware

- ...

- 0xF000 0xF7FF: Session#30 hardware

- 0xF800 0xFFFF: Session#31 hardware

The five upper bits are applied to select one of thirty-two TOE10GLL-IPs + UserRegs. More details of register map in 32-session demo is shown in Table 2-1.

### Table 2-1 Register map Definition

| Address                                        | Register Name                                                             | Description                                                                                                                      |  |  |

|------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| Wr/Rd                                          | (Label in "toe10gll32test.c")                                             |                                                                                                                                  |  |  |

| BA+0x0000 – BA+0x01FF: TOE10GLL-IP#0 interface |                                                                           |                                                                                                                                  |  |  |

|                                                |                                                                           | 00 – BA+0x03FF: LL10GEMAC-IP#0 interface                                                                                         |  |  |

|                                                | <u> </u>                                                                  | are described in TOE10GLL-IP and LL10GEMAC-IP datasheet.                                                                         |  |  |

|                                                | BA+0x0000 – BA+0x0                                                        | 0FF: Input signals of TOE10GLL-IP#0 (Write access only)                                                                          |  |  |

| BA+0x0000                                      | TOE_RST_INTREG                                                            | [0]: Mapped to RstB of TOE10GLL-IP                                                                                               |  |  |

| BA+0x0004                                      | TOE_OPM_INTREG                                                            | [1:0]: Mapped to DstMacMode of TOE10GLL-IP                                                                                       |  |  |

|                                                |                                                                           | [16]: Mapped to ARPICMPEn of TOE10GLL-IP                                                                                         |  |  |

| BA+0x0008                                      | TOE_SML_INTREG                                                            | [31:0]: Mapped to SrcMacAddr[31:0] of TOE10GLL-IP                                                                                |  |  |

| BA+0x000C                                      | TOE_SMH_INTREG                                                            | [15:0]: Mapped to SrcMacAddr[47:32] of TOE10GLL-IP                                                                               |  |  |

| BA+0x0010                                      | TOE_DMIL_INTREG                                                           | [31:0]: Mapped to DstMacAddr[31:0] of TOE10GLL-IP                                                                                |  |  |

| BA+0x0014                                      | TOE_DMIH_INTREG                                                           | [15:0]: Mapped to DstMacAddr[47:32] of TOE10GLL-IP                                                                               |  |  |

| BA+0x0018                                      | TOE_SIP_INTREG                                                            | [31:0]: Mapped to SrcIPAddr of TOE10GLL-IP                                                                                       |  |  |

| BA+0x001C                                      | TOE_DIP_INTREG                                                            | [31:0]: Mapped to DstIPAddr of TOE10GLL-IP                                                                                       |  |  |

| BA+0x0020                                      | TOE_TMO_INTREG                                                            | [31:0]: Mapped to TimeOutSet of TOE10GLL-IP [1:0]: Mapped to TCPCmd of TOE10GLL-IP. When this register is written,               |  |  |

| BA+0x0040                                      | TOE_CMD_INTREG                                                            | TCPCmdValid of TOE10GLL-IP is asserted to '1' for one cycle.                                                                     |  |  |

| BA+0x0044                                      | TOE_SPN_INTREG                                                            | [15:0]: Mapped to TCPSrcPort[15:0] of TOE10GLL-IP                                                                                |  |  |

| BA+0x0044                                      | TOE_DPN_INTREG                                                            | [15:0]: Mapped to TCPDstPort[15:0] of TOE10GLL-IP                                                                                |  |  |

| BA+0x0040                                      | TOE_TIC_INTREG                                                            | [0]: Set '1' to clear read value of TOE_STS_INTREG[2]                                                                            |  |  |

| Britioxocco                                    | 102_110_1111120                                                           | (TOE10GLL-IP interrupt)                                                                                                          |  |  |

|                                                | BA+0x0100 – BA+0x01                                                       | FF: Output signals of TOE10GLL-IP#0 (Read access only)                                                                           |  |  |

| BA+0x0100                                      | TOE_VER_INTREG                                                            | [31:0]: Mapped to IP version of TOE10GLL-IP                                                                                      |  |  |

| BA+0x0104                                      | TOE_STS_INTREG                                                            | [0]: Mapped to InitFinish of TOE10GLL-IP                                                                                         |  |  |

|                                                |                                                                           | [1]: Mapped to TCPConnOn of TOE10GLL-IP                                                                                          |  |  |

|                                                |                                                                           | [2]: TOE10GLL-IP Interrupt. Asserted to '1' when IPInt of TOE10GLL-IP is                                                         |  |  |

|                                                |                                                                           | asserted to '1'. This flag is cleared by TOE_TIC_INTREG.                                                                         |  |  |

|                                                |                                                                           | [20:16]: Mapped to IPState of TOE10GLL-IP                                                                                        |  |  |

| BA+0x0108                                      | TOE_INT_INTREG                                                            | [31:0]: Mapped to IntStatus of TOE10GLL-IP                                                                                       |  |  |

| BA+0x010C                                      | TOE_DMOL_INTREG                                                           | [31:0]: Mapped to DstMacAddrOut[31:0] of TOE10GLL-IP                                                                             |  |  |

| BA+0x0110                                      | TOE_DMOH_INTREG                                                           | [15:0]: Mapped to DstMacAddrOut[47:32] of TOE10GLL-IP                                                                            |  |  |

|                                                | BA+0x0200 – BA+0x03                                                       | BFF: Output signals of LL10GEMAC-IP (Read access only)                                                                           |  |  |

| BA+0x0200                                      | EMAC_VER_INTREG                                                           | [31:0]: Mapped to IP version of DG LL10GEMAC-IP                                                                                  |  |  |

| BA+0x0204                                      | EMAC_STS_INTREG                                                           | [0]: Mapped to Linkup of LL10GEMAC-IP                                                                                            |  |  |

|                                                | BA+ BA+0x0400 – BA+0x07FF: UserDataGen#0 and UserDataVer#0 interface      |                                                                                                                                  |  |  |

|                                                | BA+0x0400 – BA+0x04FF: Input signals of UserDataGen#0 (Write access only) |                                                                                                                                  |  |  |

| BA+0x0400                                      | USRTX_CMD_INTREG                                                          | [0]: Start flag to generate test data by UserDataGen. Set '1' to start sending data.                                             |  |  |

|                                                |                                                                           | This flag is auto-cleared after running the operation.                                                                           |  |  |

|                                                |                                                                           | [1]: Set '1' to clear USRTX_LENL/H_INTREG and USRTX_TMR_INTREG.                                                                  |  |  |

| BA+0x0420                                      | USRTX_PKL_INTREG                                                          | [10:0]: Packet length in byte unit for assigning TCPTxPkLen, input of TOE10GLL-IP.                                               |  |  |

| BA+0x0424                                      | USRTX_PSH_INTREG                                                          | [0]: PSH flag for assigning TCPTxPSH, input of TOE10GLL-IP                                                                       |  |  |

| BA+0x0428                                      | USRTX_TDL_INTREG                                                          | [31:0]: Bit[31:0] of total size in byte unit to generate test data by UserDataGen. The value is cleared by USRTX_CMD_INTREG[1].  |  |  |

| BA+0x042C                                      | USRTX_TDH_INTREG                                                          | [15:0]: Bit[47:32] of total size in byte unit to generate test data by UserDataGen. The value is cleared by USRTX_CMD_INTREG[1]. |  |  |

| WiRd   (Label in Too10gli32test.c*)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Address                 | Register Name                  | Description                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BA+0x0500 BA+0x050F Couput signals of UserDataGen#0 (Read access only)  BA+0x0504 USRTX_STS_INTREG [0]: Busy signal of UserDataGen (0'-dio, "1-Data is transmitting)  BA+0x0504 USRTX_TMR_INTREG [0]: Busy signal of UserDataGen (0'-dio, "1-Data is transmitting)  BA+0x0508 USRTX_LENL_INTREG [1]: The value is cleared by USRTX_CMD_INTREG [1]:  BA+0x0508 USRTX_LENL_INTREG [31:0]: Bigi31:0] of complete size of transmitted data in byte unit which is calculated by the sum of TCPTxCplLen, output from TOE10GLL-IP. The value is cleared by USRTX_CMD_INTREG [1]:  BA+0x050C USRTX_LENH_INTREG [31:0]: Bigi31:0] of complete size of transmitted data in byte unit which is calculated by the sum of TCPTxCplLen, output from TOE10GLL-IP. The value is cleared by USRTX_CMD_INTREG [1]:  BA+0x0500 —BA+0x06FF: Input signals of UserDataVer(0'-Wite access only)  BA+0x0600 —BA+0x06FF: Input signals of UserDataVer(0'-Wite access only)  BA+0x0600 —BA+0x0FFF: Output signals of UserDataVer(0'-Wite access only)  BA+0x0600 —BA+0x0FFF: Output signals of UserDataVer(0'-Wite access only)  BA+0x0600 —BA+0x0FFF: Output signals of UserDataVer(0'-Wite access only)  BA+0x0700 —USRRX_STS_INTREG [0]: Set '1' to clear read value of USRRX_STS_INTREG(1)  BA+0x0704 USRRX_STS_INTREG [0]: Set '1' to clear read value of USRRX_STS_INTREG(1)  BA+0x0704 USRRX_STS_INTREG [1]: Receive data is incorrect)  BA+0x0705 USRRX_STS_INTREG [1]: Receive data is processed user of the processed use |                         |                                | 2 description                                                                                                                                                |

| BA+0x0500   USRTX_STS_INTREG   (i): Buys signal of UserDataGen ("0-Ider, "1-Data is transmitting)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         | •                              | F: Output signals of UserDataGen#0 (Read access only)                                                                                                        |

| BA+0x0504   USRTX_TMR_INTREG   Timer value which shows latency time in Tx interface of TOE:10GLL-IP (15:0); Tx latency time of TOE:10GLL-IP clock cycle unit The value is cleared by USRTX_CMD_INTREG [1].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BA+0x0500               |                                |                                                                                                                                                              |

| BA+0x0508   USRTX_LENL_INTREG G   [31:0]: Bit[31:0] of complete size of transmitted data in byte unit which is calculated by the sum of TCPTXCpLen, output from TOE10GLL-IP. The value is cleared by USRTX CMD. INTREG [1].    BA+0x0500   USRTX_LENH_INTREG   [15:0]: Bit[47:32] of complete size of transmitted data in byte unit which is calculated by the sum of TCPTXCpLen, output from TOE10GLL-IP. The value is cleared by USRTX_CMD. INTREG [1].    BA+0x0600   BA+0x0600   BA+0x06FF: Input signals of UserDataVer#0 (Write access only)   BA+0x0600   USRRX_CMD_INTREG   [0]: Enable data verification of UserDataVer (V: Disable data verification)   [1]: Set 1" to clear usRRX_LENL/H_INTREG and USRRX_TMR_INTREG are reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |                                | Timer value which shows latency time in Tx interface of TOE10GLL-IP [15:0]: Tx latency time of TOE10GLL-IP in clock cycle unit                               |

| BA+0x050C   USRTX_LENH_INTREG   15:0]: Bitl47:32] of complete size of transmitted data in byte unit which is calculated by the sum of TCPTxCplLen, output from TOE10GLL-IP. The value is cleared by USRTX_CMD_INTREG [1].    BA+0x0600                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BA+0x0508               | USRTX_LENL_INTREG G            | [31:0]: Bit[31:0] of complete size of transmitted data in byte unit which is calculated by the sum of TCPTxCplLen, output from TOE10GLL-IP.                  |

| BA+0x0600 - BA+0x06FF: Input signals of UserDataVer#0 (Write access only)  BA+0x0600  USRRX_CMD_INTREG  [0]: Enable data verification of UserDataVer#0 (Write access only)  [1]: Set '1' to clear USRRX_LENL/H_INTREG and USRRX_TMR_INTREG are reset.  BA+0x0604  USRRX_RXC_INTREG  [0]: Set '1' to clear read value of USRRX_STS_INTREG[1]  (TCPRxError of TOE10GLL-IP)  BA+0x0700 - BA+0x070FF: Output signals of UserDataVer#0 (Read access only)  [1]: Receive error interrupt. Asserted to '1' when TCPRxError fror TOE10GLL-IP shows error status. This flag can be cleared by USRRX_RXC_INTREG.  BA+0x0704  USRRX_TMR_INTREG  Imer value which shows latency time in Rx interface of TOE10GLL-IP [15:0]: Rx Latency time of TOE10GLL-IP in clock cycle unit. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0708  USRRX_ERR_INTREG  [7:0]: Latch signal of TCPRxError, output of TOE10GLL-IP. The value does not change after detecting error. The value is reset after this register is read by CPU.  BA+0x0720  USRRX_LENL_INTREG  [31:0]: Bit[31:0] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0724  USRRX_ENL_INTREG  [15:0]: Bit[31:0] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0728  USRRX_FAILPOSL_INTREG  [31:0]: Bit[31:0] of this first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0720  USRRX_FAILPOSL_INTREG  [31:0]: Expected data that IP should receive when data verification is failed.  BA+0x0730  USRRX_EXPPAT_INTREG  [31:0]: Expected data that IP should receive when data verification is failed.  BA+0x0700-  Similar to BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, an BA+0x1000-  Similar to BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, an BA+0x1000-  BA+0x17FF  BA+0x4000-  This area i | BA+0x050C               | USRTX_LENH_INTREG              | [15:0]: Bit[47:32] of complete size of transmitted data in byte unit which is calculated by the sum of TCPTxCplLen, output from TOE10GLL-IP.                 |

| BA+0x0600 USRRX_CMD_INTREG [0]: Enable data verification of UserDataVer (0°: Disable data verification) [1]: Set "1" to clear USRRX_LENL/H_INTREG and USRRX_TMR_INTREG are reset.  BA+0x0604 USRRX_RXC_INTREG [0]: Set "1" to clear read value of USRRX_STS_INTREG[1] (TCPRxError of TOE10GLL-IP)  BA+0x0700 = BA+0x07FF: Output signals of UserDataVer#0 (Read access only)  BA+0x0700 USRRX_STS_INTREG [0]: Verify fail (0°-No error, "1"-Received data is incorrect) [1]: Receive data in Experiment [1]: Receive data in E |                         | BA+0x0600 – BA+0x06            |                                                                                                                                                              |

| BA+0x0700                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BA+0x0600               | USRRX_CMD_INTREG               | ('0': Disable data verification, '1': Enable data verification) [1]: Set '1' to clear USRRX_LENL/H_INTREG and USRRX_TMR_INTREG                               |

| BA+0x0700 USRRX_STS_INTREG [0]: Verify fail (10'-No error, '1'-Received data is incorrect) [1]: Receive error interrupt. Asserted to '1' when TCPRxError fror TOE10GLL-IP shows error status. This flag can be cleared by USRRX_RXC_INTREG.  BA+0x0704 USRRX_TMR_INTREG Timer value which shows latency time in Rx interface of TOE10GLL-IP [15:0]: Rx Latency time of TOE10GLL-IP in clock cycle unit. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0708 USRRX_ERR_INTREG [7:0]: Latch signal of TCPRxError, output of TOE10GLL-IP. The value does not change after detecting error. The value is reset after this register is read by USRRX_CMD_INTREG[1].  BA+0x0720 USRRX_LENL_INTREG [31:0]: Bit[31:0] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0724 USRRX_EXPLENL_INTREG [15:0]: Bit[47:32] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0728 USRRX_FAILPOSL_INTREG [31:0]: Bit[31:0] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0720 USRRX_FAILPOSH_INTREG [31:0]: Bit[47:32] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0730 USRRX_EXPPAT_INTREG [31:0]: Expected data that IP should receive when data verification is failed.  BA+0x0731 USRRX_EXPPAT_INTREG [31:0]: Expected data that IP should receive when data verification is failed.  BA+0x0767 UserDataVer for operating Session#3. Lt.10EMAC-IP area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#3. Lt.10EMAC-IP area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#3. Lt.10EMAC-IP area is mapped the same data as Session#0.  BA+0x0800-BA+0x0800-BA+0x0800-BA+0x0800-BA+0x0800-BA+0x0800-BA+0x0800-BA+0x0800-BA+0x0800-BA+0x0800-BA+0x0800-BA+0x0800-B | BA+0x0604               | USRRX_RXC_INTREG               |                                                                                                                                                              |

| 11   Receive error interrupt. Asserted to '1' when TCPRxError fror TOE10GLL-IP shows error status. This flag can be cleared by USRRX_RXO_INTREG.    BA+0x0704   USRRX_TMR_INTREG   Timer value which shows latency time in Rx interface of TOE10GLL-IP [15:0]: Rx Latency time of TOE10GLL-IP in clock cycle unit. The value is cleared by USRRX_CMD_INTREG[1].    BA+0x0708   USRRX_ERR_INTREG   [7:0]: Latch signal of TCPRxError, output of TOE10GLL-IP. The value does not change after detecting error. The value is reset after this register is read to CPU.    BA+0x0720   USRRX_LENL_INTREG   [31:0]: Bit[31:0] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].    BA+0x0724   USRRX_LENH_INTREG   [15:0]: Bit[47:32] of tourrent size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].    BA+0x0728   USRRX_FAILPOSL_INTREG   [31:0]: Bit[31:0] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG[1].    BA+0x0720   USRRX_FAILPOSH_INTREG   [31:0]: Bit[47:32] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG[1].    BA+0x0730   USRRX_EXPPAT_INTREG   [31:0]: Expected data that IP should receive when data verification is failed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         | BA+0x0700 – BA+0x07F           | F: Output signals of UserDataVer#0 (Read access only)                                                                                                        |

| [15:0]: Rx Latency time of TOE10GLL-IP in clock cycle unit. The value is cleared by USRRX_CMD_INTREG[1].  [7:0]: Latch signal of TCPRxError, output of TOE10GLL-IP. The value does not change after detecting error. The value is reset after this register is read by CPU.  [7:0]: Latch signal of TCPRxError, output of TOE10GLL-IP. The value does not change after detecting error. The value is reset after this register is read by CPU.  [84:00720]  [85:0]: Bit[31:0] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].  [86:0]: Bit[47:32] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].  [87:0]: Bit[47:32] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].  [88-40x0728]  [87:0]: Bit[31:0] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG[1].  [88-40x0720]  [89-40x0720]  [89-40x0721]  [89-40x0722]  [89-40x0723]  [89-40x0723]  [89-40x0724]  [89-40x0724]  [89-40x0725]  [89-40x0725]  [89-40x0726]   | BA+0x0700               | USRRX_STS_INTREG               | [1]: Receive error interrupt. Asserted to '1' when TCPRxError from TOE10GLL-IP shows error status. This flag can be cleared by.                              |

| BA+0x0708 USRRX_ERR_INTREG [7:0]: Latch signal of TCPRxError, output of TOE10GLL-IP. The value does not change after detecting error. The value is reset after this register is read by CPU.  BA+0x0720 USRRX_LENL_INTREG [31:0]: Bit[31:0] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0724 USRRX_ENH_INTREG [15:0]: Bit[47:32] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0728 USRRX_FAILPOSL_INTREG [31:0]: Bit[31:0] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0720 USRRX_FAILPOSH_INTREG [15:0]: Bit[47:32] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0730 USRRX_EXPPAT_INTREG [31:0]: Expected data that IP should receive when data verification is failed.  BA+0x0800- BA+0x0800- BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#1. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1800- BA+0x17FF BA+0x0000 - BA+0x07FF, but this area is mapped the same data as Session#0.  BA+0x1800- BA+0x17FF BA+0x0000 - BA+0x07FF, but this area is mapped the same data as Session#0.  BA+0x1800- BA+0x17FF BA+0x0000 - BA+0x07FF, but this area is mapped the same data as Session#0.  BA+0x1800- BA+0x1800- BA+0x007FF, but this area is mapped the same data as Session#0.  BA+0x1800- BA+0x1800- BA+0x07FF, but this area is mapped the same data as Session#0.  BA+0x1800- BA+0x1800- BA+0x07FFF but this area is mapped the same data as Session#0.  BA+0x1800- BA+0x1800- BA+0x0000- BA+0x07FFF, but this area is mapped the same data as Session#0.  BA+0x1800- BA+0x1800- BA+0x07FFF but this area is mapped the same data as Session#0.  BA+0x1800- BA+0x1800- BA+0x1800- BA+0x1800- BA+0x1800- BA+0x1800- BA+ | BA+0x0704               | USRRX_TMR_INTREG               | [15:0]: Rx Latency time of TOE10GLL-IP in clock cycle unit.                                                                                                  |

| when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG[1].  BA+0x0724 USRRX_LENH_INTREG [15:0]: Bit[47:32] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0728 USRRX_FAILPOSL_INTREG [31:0]: Bit[31:0] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x072C USRRX_FAILPOSH_INTREG [15:0]: Bit[47:32] of the first position in byte unit that data verification detect failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0730 USRRX_EXPPAT_INTREG [31:0]: Received data that IP should receive when data verification is failed.  BA+0x0734 USRRX_RDPAT_INTREG [31:0]: Received data that is incorrect when data verification is failed.  BA+0x0800- BA+0x8000- BA+0 | BA+0x0708               | USRRX_ERR_INTREG               | [7:0]: Latch signal of TCPRxError, output of TOE10GLL-IP. The value does not change after detecting error. The value is reset after this register is read by |

| BA+0x0724 USRRX_LENH_INTREG [15:0]: Bit[47:32] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0728 USRRX_FAILPOSL_INTREG [31:0]: Bit[31:0] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x072C USRRX_FAILPOSH_INTREG [15:0]: Bit[47:32] of the first position in byte unit that data verification detect failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0730 USRRX_EXPPAT_INTREG [31:0]: Expected data that IP should receive when data verification is failed.  BA+0x0734 USRRX_RDPAT_INTREG [31:0]: Received data that is incorrect when data verification is failed.  BA+0x0800 BA+0xFFFF: Register Area of Session#1 - Session#31  BA+0x0800 BA+0x0800 BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#1. LL10EMAC-IP area is mapped the same data as Session#0.  BA-0x17FF UserDataVer for operating Session#2. LL10EMAC-IP area is mapped the same data as Session#0.  BA-0x1800 BA+0x1800 BA+0x0000 BA+0x07FF, but this area is mapped the same data as Session#0.  BA-0x18FF UserDataVer for operating Session#3. LL10EMAC-IP area is mapped the same data as Session#0.  BA-0x18FF BA+0x2000 BA+0x07FF Session#4 - Session#7.  BA-0x4000 This area is mapped to Session#8 - Session#15.  BA+0x40000 This area is mapped to Session#16 - Session#31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BA+0x0720               | USRRX_LENL_INTREG              | ·                                                                                                                                                            |

| BA+0x0728 USRRX_FAILPOSL_INTREG [31:0]: Bit[31:0] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x072C USRRX_FAILPOSH_INTREG [15:0]: Bit[47:32] of the first position in byte unit that data verification detect failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0730 USRRX_EXPPAT_INTREG [31:0]: Expected data that IP should receive when data verification is failed.  BA+0x0734 USRRX_RDPAT_INTREG [31:0]: Received data that is incorrect when data verification is failed.  BA+0x0800 BA+0xFFFF: Register Area of Session#1 - Session#31  BA+0x0800 Similar to BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#1. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1000 Similar to BA+0x0000 - BA+0x07FF, but this area is mapped the same data as Session#0.  BA+0x1800 Similar to BA+0x0000 - BA+0x07FF, but this area is mapped the same data as Session#0.  BA+0x1800 Similar to BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#2. LL10EMAC-IP area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#3. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x2000 This area is mapped to Session#4 - Session#7.  BA+0x4000 This area is mapped to Session#8 - Session#15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BA+0x0724               | USRRX_LENH_INTREG              | [15:0]: Bit[47:32] of current size of received data in byte unit which is counted when the packet received from TOE10GLL-IP is valid.                        |

| failure. The value is cleared by USRRX_CMD_INTREG [1].  BA+0x0730  USRRX_EXPPAT_INTREG [31:0]: Expected data that IP should receive when data verification is failed.  BA+0x0734  USRRX_RDPAT_INTREG [31:0]: Received data that is incorrect when data verification is failed.  BA+0x0800  BA+0x0FFF: Register Area of Session#1 — Session#31  BA+0x0800  Similar to BA+0x0000  BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and BA-0x0FFF UserDataVer for operating Session#1. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1000  Similar to BA+0x0000  BA+0x07FF, but this area is mapped the same data as Session#0.  BA-0x17FF  UserDataVer for operating Session#2. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1800  Similar to BA+0x0000  BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and BA-0x1FFF  UserDataVer for operating Session#3. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x2000  This area is mapped to Session#4 — Session#7.  BA+0x4000  This area is mapped to Session#8 — Session#15.  BA+0x8000  This area is mapped to Session#16 — Session#31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | BA+0x0728               | USRRX_FAILPOSL_INTREG          | [31:0]: Bit[31:0] of the first position in byte unit that data verification detects                                                                          |

| BA+0x0734 USRRX_RDPAT_INTREG [31:0]: Received data that is incorrect when data verification is failed.  BA+0x0800 - BA+0xFFFF: Register Area of Session#1 - Session#31  BA+0x0800- Similar to BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, an UserDataVer for operating Session#1. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1000- Similar to BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, an UserDataVer for operating Session#2. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1800- Similar to BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, an UserDataVer for operating Session#3. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x2000- BA+0x2000- This area is mapped to Session#4 - Session#7.  BA+0x4000- This area is mapped to Session#8 - Session#15.  BA+0x8000- This area is mapped to Session#16 - Session#31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BA+0x072C               | USRRX_FAILPOSH_INTREG          | [15:0]: Bit[47:32] of the first position in byte unit that data verification detects failure. The value is cleared by USRRX_CMD_INTREG [1].                  |

| BA+0x0800 - BA+0xFFFF: Register Area of Session#1 - Session#31  BA+0x0800- BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and BA-0x0FFF UserDataVer for operating Session#1. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1000- BA+0x1000- BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and BA+0x1800- BA+0x1800- BA+0x1800- BA+0x1800- BA+0x0000- BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#3. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x2000- BA+0x2000- BA+0x2000- BA+0x4000- BA+0x4000- BA+0x4000- This area is mapped to Session#8 - Session#15.  BA+0x8000- This area is mapped to Session#16 - Session#31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |                                |                                                                                                                                                              |

| BA+0x0800- BA+0x0800- BA+0x00FFF  BA+0x1000- BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, an UserDataVer for operating Session#1. LL10EMAC-IP area is mapped to TOE10GLL-IP, UserDataGen, an UserDataVer for operating Session#2. LL10EMAC-IP area is mapped to TOE10GLL-IP, UserDataGen, an UserDataVer for operating Session#2. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1800- BA+0x1800- BA+0x2000- BA+0x2000- BA+0x2000- BA+0x2000- BA+0x4000- BA+0x4000- BA+0x4000- BA+0x4000- BA+0x4000- BA+0x4000- BA+0x8000- This area is mapped to Session#16 – Session#31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BA+0x0734               |                                |                                                                                                                                                              |

| BA-0x0FFF UserDataVer for operating Session#1. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1000- Similar to BA+0x0000 – BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, an UserDataVer for operating Session#2. LL10EMAC-IP area is mapped to TOE10GLL-IP, UserDataGen, an BA+0x1800- Similar to BA+0x0000 – BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, an UserDataVer for operating Session#3. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x2000- BA+0x2000- This area is mapped to Session#4 – Session#7.  BA+0x4000- BA+0x4000- This area is mapped to Session#16 – Session#15.  BA+0x8000- This area is mapped to Session#16 – Session#31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DA 10:0000              |                                |                                                                                                                                                              |

| BA+0x1000- BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#2. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1800- BA+0x1800- BA+0x0000 - BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, and UserDataVer for operating Session#3. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x2000- BA+0x2000- BA+0x4000- BA+0x4000- BA+0x4000- BA+0x4000- BA+0x4000- This area is mapped to Session#16 - Session#31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         |                                |                                                                                                                                                              |

| BA-0x17FF UserDataVer for operating Session#2. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x1800- Similar to BA+0x0000 – BA+0x07FF, but this area is mapped to TOE10GLL-IP, UserDataGen, an UserDataVer for operating Session#3. LL10EMAC-IP area is mapped the same data as Session#0.  BA+0x2000- BA+0x2000- BA+0x3FFF  BA+0x4000- This area is mapped to Session#8 – Session#15.  BA+0x8000- This area is mapped to Session#16 – Session#31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         | ·                              |                                                                                                                                                              |

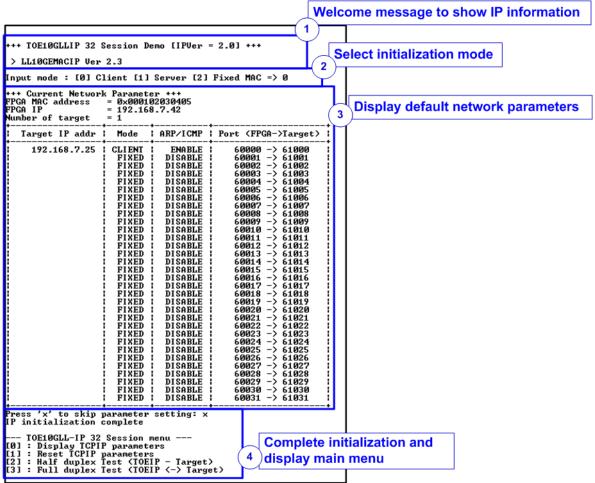

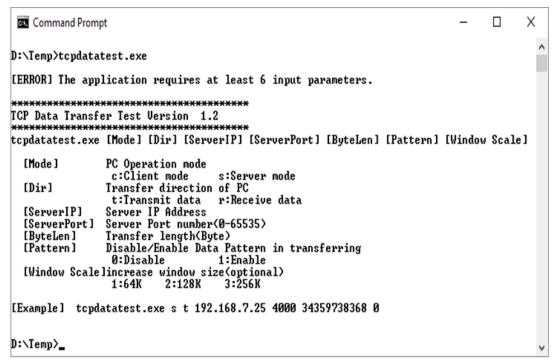

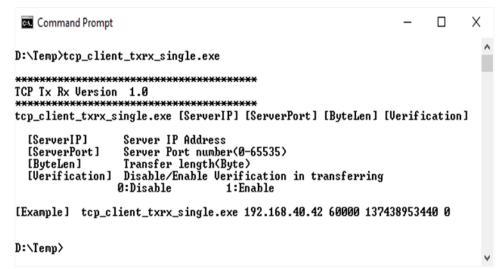

| BA+0x1800- BA-0x1FFF  BA+0x2000- BA+0x3FFF  BA+0x4000- BA+0x4000- BA+0x4000- BA+0x8000- BA+0x8000- BA+0x8000- BA+0x8000- BA+0x0000- BA+0x07FFF  BA+0x8000- BA+0x0000- BA+0x07FFF  BA+0x8000- BA+0x0000- BA+0x07FFF, but this area is mapped to TOE10GLL-IP, UserDataGen, and UserDataGen, a |                         |                                |                                                                                                                                                              |