# TOE10G-IP マルチセッション・デモ手順書(Altera 版)

Rev1.0J 2017/01/11

このドキュメントは TOE10G-IP コアを使い複数の TCP セッションを同時に実行する実機デモです。 TOE10G-IP コアを実装した Altera 製 FPGA 評価ボード(Arria10SoC 開発キット)を 10Gbit イーサネットで PC と通信します。 PC 側では最大 8 セッションを同時に実行し各セッションが独立して FPGA と通信します。 本デモのパケット・サイズはジャンボ・フレーム・サイズとなります。

### 1 動作環境

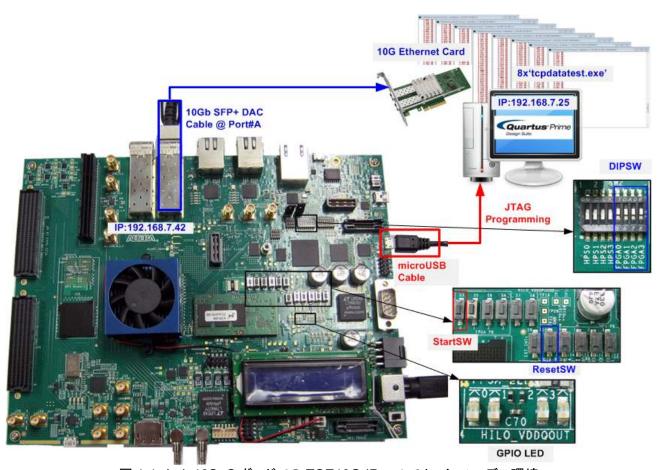

TOE10G-IP マルチセッションのデモ動作環境を図 1-1 に示します。以下の部材を用意してください。

- 1) Altera 製 FPGA ボード (Arria10 SoC 開発キット)

- 2) 10Gbit イーサネットのポートを持つか、または 10 ギガビット・イーサネット・カードを装着した Windows PC

- 3) FPGA ボードと PC 間を接続する 10Gbit SFP+光トランシーバおよび光ケーブルまたは SFP+ダイレクト・ア タッチ・ケーブル

- 4) FPGA ボード付属の JTAG 接続用 micro USB ケーブル

- 5) PC の Dos ウインドウで動作する"tcpdatatest.exe" (DesignGateway 社 Web ページからダウンロード)

<u>図 1-1: Arria10SoC ボードでの TOE10G-IP マルチセッション・デモ環境</u>

注意: 本ドキュメントで例示された実機動作結果は以下のテスト環境にて実測されたものです。

- [1] 10G ネットワーク・アダプタ: Intel X520-DA2

- http://ark.intel.com/ja/products/39776/Intel-Ethernet-Converged-Network-Adapter-X520-DA2

- [2] 10Gbit SFP+ ダイレクト・アタッチ・ケーブル (ケーブル長 1m)

- http://www.netgear.com/business/products/switches/modules-accessories/axc761.aspx

- [3] PC: Motherboard Z170-K, 32 GB RAM, 64-bit Windows7 OS, CPU i7-6700K@4.00 GHz

# 2 マルチセッション・デモの説明

本デモでは PC から最大 8 セッションの送信あるいは受信動作を実行できます。 各セッションの転送方向は FPGA ボード上 DIPSW にて bit5-8 の 4 ビットで決めます。 下表 2-1 のように DIPSW の 1 ビットにつき 2 セッションの転送方向を指定します。

図 2-1: 本デモで使う DIPSW5-8 の 4 ビット(FPGA3-1 のシルク)

| DIPSW | OFF (Logic='1')               | ON (Logic='0')               |

|-------|-------------------------------|------------------------------|

| 5     | Port#4000 と#4001 は PC からの受信方向 | Port#4000 と#4001 は PC への送信方向 |

| 6     | Port#4002 と#4003 は PC からの受信方向 | Port#4002 と#4003 は PC への送信方向 |

| 7     | Port#4004 と#4005 は PC からの受信方向 | Port#4004 と#4005 は PC への送信方向 |

| 8     | Port#4006 と#4007 は PC からの受信方向 | Port#4006 と#4007 は PC への送信方向 |

表 2-1: DIPSW bit5-8 の 4 ビットによる各ポートの転送方向定義

図 2-2: デモの状態を示す 4 ビットの LED

4ビットの LED がハードウエアの状態を示します。FPGA ボードの LED 定義を下表 2-2 に示します。

| LED | ON/BLINK(点滅)                       | OFF                                                                  |

|-----|------------------------------------|----------------------------------------------------------------------|

| 0   | ON: IPコアの初期化が完了                    | 初期化が未完了<br>スタート SW(S3)を押下したこと、および PC の IP アドレス設定が正<br>しいことを確認してください。 |

| 1   | 点滅: 1 つまたは複数のセッションでタ<br>イムアウトが発生した | 正常動作                                                                 |

| 2   | 未使用                                | 未使用                                                                  |

| 3   | ON: 1 つまたは複数のセッションでコネ<br>クションが確立した | コネクションは確立されていない                                                      |

表 2-2: LED 定義

# 3 デモ実施方法

本マルチセッション・デモの準備は以下の手順で進めてください。

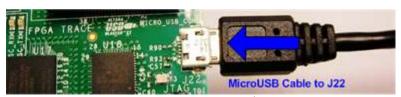

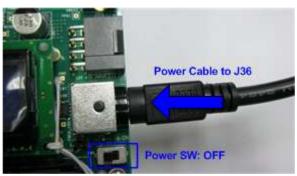

1) FPGA ボード付属のマイクロ USB ケーブルを FPGA ボードと PC 間に接続し、FPGA ボードの電源ケーブルも接続します。

図 3-1: マイクロ USB ケーブルの接続

図 3-2: 電源ケーブルの接続

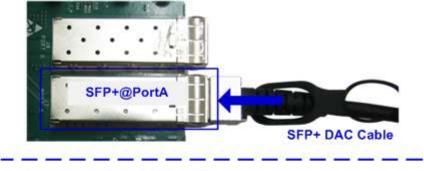

2) 10Gbit SFP+ DAC(ダイレクト・アタッチ・ケーブル)または SFP+光トランシーバ&光ケーブルを SFP+のポート A と PC 間に接続します。

図 3-3: SFP+ケーブルの接続

3) PC のネットワーク設定を"TOE10G-IP 標準デモ手順書(Altera 版)"の"3 章 PC 設定"にしたがって設定します。

参考 URL: <a href="http://www.dgway.com/products/IP/TOE10G-IP/dg">http://www.dgway.com/products/IP/TOE10G-IP/dg</a> toe10gip instruction altera jp.pdf

- 4) FPGAボードの電源を投入します。

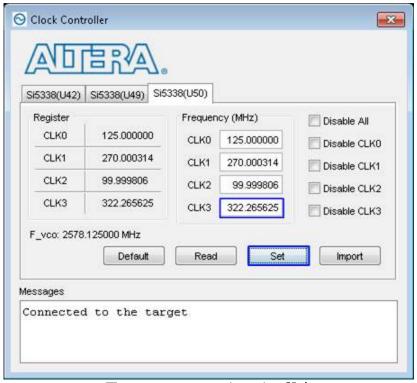

- 5) Arria10SoC 開発キット内の"Clock Controller"アプリケーションを起動します。 図 3-4 に示すように Si5338(U50)タブを選択し、CLK3 の周波数値を"322.265625"MHz にセットします。"Set"ボタンを押下し発振クロック周波数を 322.265625MHz に設定します。

図 3-4: リファレンス・クロックの設定

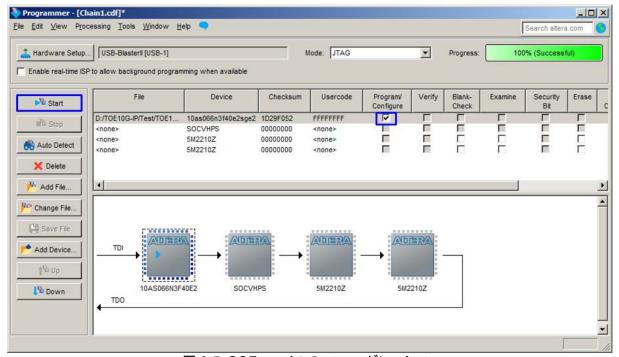

6) Quartus プログラマを起動し、デモ用 SOF ファイルを選択して図 3-5 のようにコンフィグレーションします。

図 3-5: SOF ファイルのコンフィグレーション

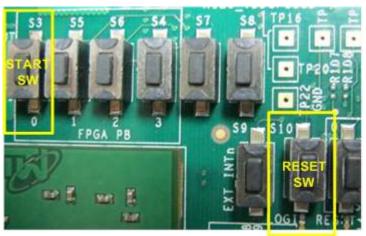

7) 図 3-6 で図示した S3 位置のスタート SW を押下してシステムの初期化を実行します。 そして図 3-7 に示すように LEDO が点灯することを確認してください。

図 3-6: スタート SW の位置

図 3-7: スタート SW 押下後の LED 状態

<u>ご注意</u>: 実機デモにおける転送パフォーマンスはテストPC のパフォーマンスに依存するため、10Gbit イーサネットの送受信を実行するに十分な能力を備えたPC を用意する必要があります。

## 4 デモ手順

最初に LED0 が点灯し IP コアが初期化プロセスを完了していることを確認してください。

本マルチセッション・デモにおいては"tcpdatatest"アプリケーションがクライアント・モードで起動され、新しいコネクションを確立します、そして FPGA 内の TOE10G-IP コアで構築されたサーバーとデータを送受信します。確立した各セッションでの送信/受信テストの詳細については以下を参照してください。

#### 4.1 データ送信テスト

このトピックでは FPGA から PC へのデータ送信テストの手順を説明します。総転送サイズは 32G バイト固定です。ユーザはポート番号をそれぞれ 4000~4007 に設定した最大 8 個の"tcpdatatest"をそれぞれ個別の DOS 窓で同時に実行することで、8 セッションまでの同時送信を検証できます。 データを送信するポートでは DIPSW の該当するビットの設定を'ON'とする必要があります。

送信テストでは各 DOS 窓にて以下のコマンド・ラインを実行してください。 >> tcpdatatest c r 192.168.7.42 <4000-4007> 0 1

ポート 4000~4007 のコネクションが確立すると LED3 が点灯します。 PC 上のコンソールでは1秒ごとに総転送サイズが表示されます。 テストのパフォーマンスは各操作の最後に表示されます。

図 4-1 にポート#4000 を使ってデータ送信テストを実行した例を示します。この場合 DIPSW の bit5 は'ON'と する必要があります。 本マルチセッション・デモのパフォーマンスは通常デモの大体 1/4 程度になりますが、それは本デモでは IP で使われているバッファ・サイズが 4K バイトであり、一方通常デモでのバッファ・サイズが64K バイトであることがその理由です。

Port number: Valid value = 4000 - 4007

D:\Share\Pat\SW\\condenset c r 192.168.7.42 (4000) 0 1

Start Receiving with Data pattern in Client mode

IP: 192.168.7.42:4000

Waiting for connection ...

System connected

Receiving Data Size ...

180.556 MB

367.192 MB

552.361 MB

735.433 MB

33.742 GB

33.980 GB

34.227 GB

Spend 152.10 Second(s) for Receiving 34.360 GByte(s)

Receiving Data Rate: 225.90 MByte(s)/Sec

D:\Share\Pat\SW\\_

図 4-1: ポート#4000 を使った送信テストと DIPSW 設定例

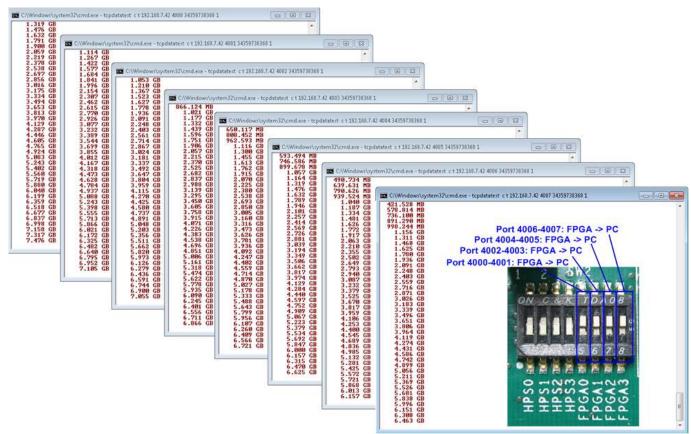

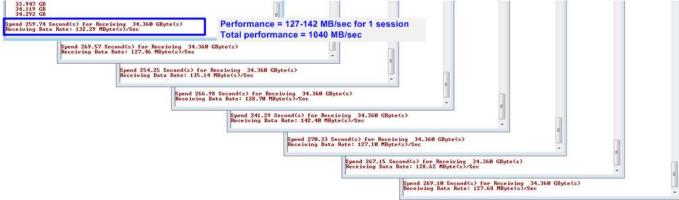

図 4-2 に最大の 8 セッションを Port#4000~4007 で同時送信した例を示します。 DIPSW の Bit5-8 はこの場合全で'ON'とします。図 4-3 に各セッションでのパフォーマンス結果を抜粋しますが1セッション当たりの送信パフォーマンスは 127MB/sec~143MB/sec です、そして全 8 セッションの合計パフォーマンスは 1046MB/sec となります。

図 4-2: 同時 8 セッションの送信テスト(PC 側では 8 個の DOS 窓でそれぞれのポートでのセッションを実行)

図 4-3: 同時 8 セッションの送信テストのパフォーマンス結果例

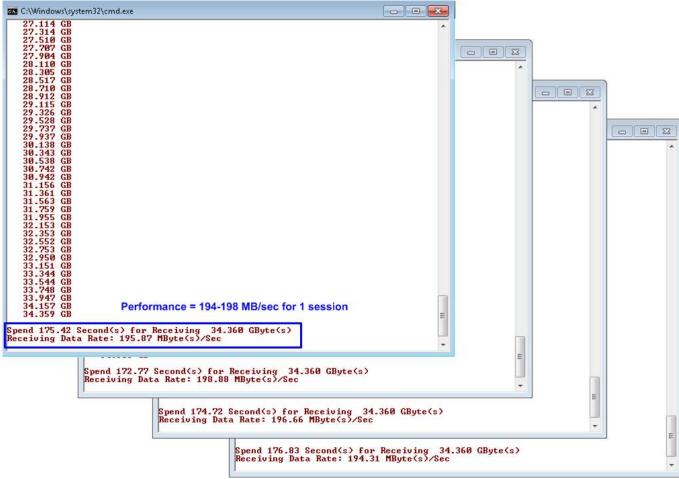

図 4-4 に 4 セッションを Port#4000~4003 で同時送信した例を示します。1 セッションのパフォーマンスは大体 194-198MB/sec ですがそれは図 4-1 に示した単一セッションの場合より 10%程度低下しています。

図 4-4: 同時 4 セッションの送信テスト(PC 側では 4 個の DOS 窓でそれぞれのポートでのセッションを実行)

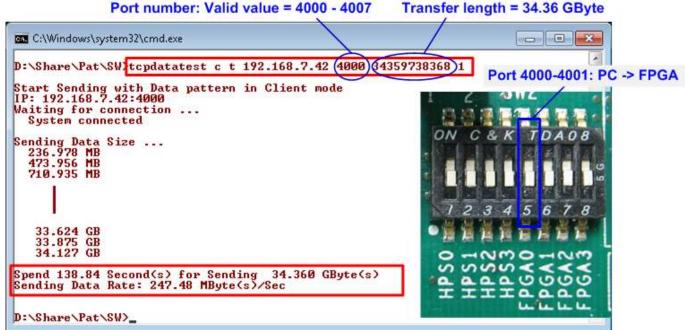

#### 4.2 データ受信テスト

このトピックではPCからFPGAへのデータ受信テストの手順を説明します。総転送サイズはテスト・アプリケーションでユーザが決めることができます。ユーザはポート番号をそれぞれ 4000~4007 に設定した最大 8 個の"tcpdatatest"をそれぞれ個別の DOS 窓で同時に実行することで、8 セッションまでの同時受信を検証できます。 データを送信するポートでは DIPSW の該当するビットの設定を'OFF'とする必要があります。

ポート 4000~4007 のコネクションが確立すると LED3 が点灯します。 PC 上のコンソールでは1秒ごとに総転送サイズが表示されます。 テストのパフォーマンスは各操作の最後に表示されます。

図 4-5 にポート#4000 を使ってデータ受信テストを実行した例を示します。この場合 DIPSW の bit5 は'OFF'と する必要があります。 本マルチセッション・デモのパフォーマンスは通常デモの大体 1/4 程度になりますが、それは本デモでは IP で使われているバッファ・サイズが 4K バイトであり、一方通常デモでのバッファ・サイズが 64K バイトであることがその理由です。

図 4-5: ポート#4000 を使った受信テストと DIPSW 設定例

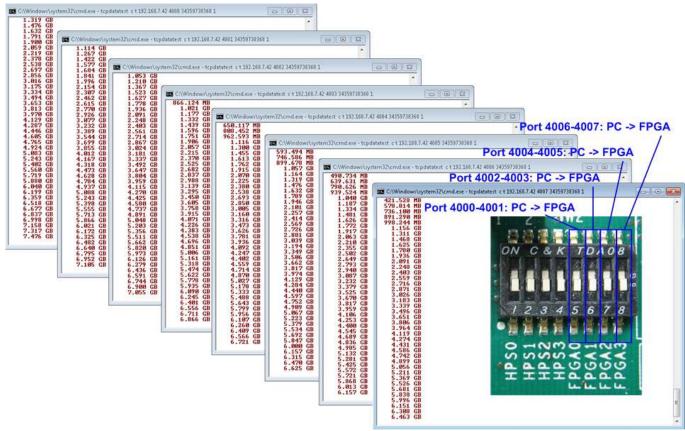

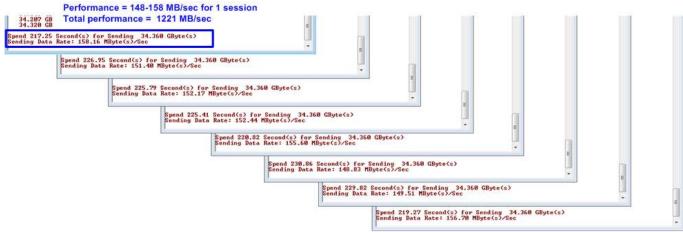

図 4-6 に最大の 8 セッションを Port#4000~4007 で同時受信した例を示します。 DIPSW の Bit5-8 はこの場合全で' OFF'とします。図 4-7 に各セッションでのパフォーマンス結果を抜粋しますが1セッション当たりの受信パフォーマンスは 148MB/sec~158MB/sec です、そして全 8 セッションの合計パフォーマンスは 1221MB/sec となります。

図 4-6: 同時 8 セッションの受信テスト(PC 側では 8 個の DOS 窓でそれぞれのポートでのセッションを実行)

図 4-7: 同時 8 セッションの受信テストのパフォーマンス結果例

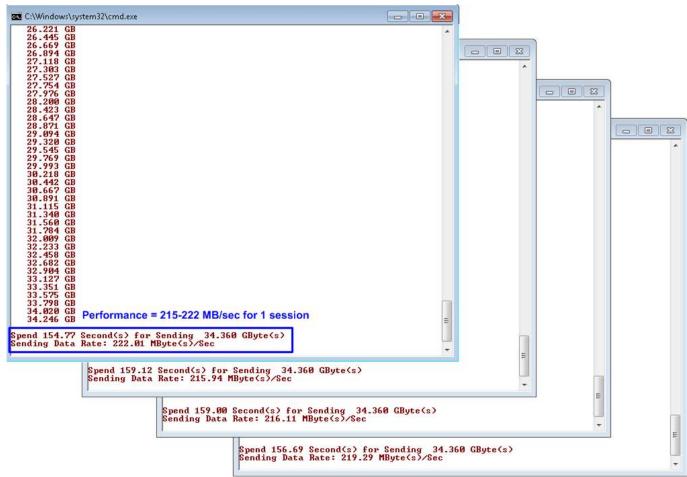

図 4-8 に 4 セッションを Port#4000~4003 で同時受信した例を示します。1 セッションのパフォーマンスは大体 215-222MB/sec ですがそれは図 4-5 に示した単一セッションの場合より 10%程度低下しています。

図 4-8: 同時 4 セッションの受信テスト(PC 側では 4 個の DOS 窓でそれぞれのポートでのセッションを実行)

#### 4.3 データ送受信テスト

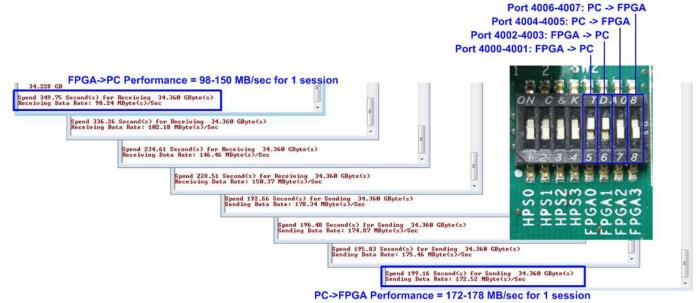

4 ビットの DIPSW を異なる設定とすることで異なるポートごとに送信・受信の方向を変えて同時通信することができます。

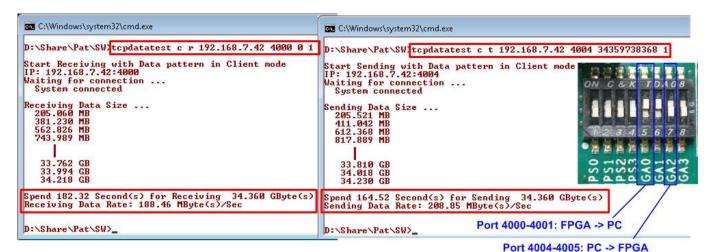

図 4-9 および図 4-10 に送受信テストを同時 2 セッションと同時 8 セッションで実行した例を示します。

図 4-9: 同時 2 セッションの送受信テスト

図 4-10: 同時 8 セッションの送受信テスト

# 5 更新履歴

| リビジョン | 日付         | 履歴            |

|-------|------------|---------------|

| 1.0J  | 2017/01/11 | 初期リリース版の日本語翻訳 |

|       |            |               |