# UDP1G-IP リファレンス・デザイン説明書 (Intel 版)

Rev1.0J 2017/03/21

### 1. UDP プロトコル概要

TCP と比較すると UDP プロトコルは最小限のプロトコル・メカニズムでメッセージの送信を可能としています、ただしハンドシェークがないためデータは保証されません。 TCP と同様 UDP においてもデータ内容の信頼性確認のためチェック・サム機能を持ち、データ送受信ダイヤグラムで異なる機能をアドレッシングするためポート番号が用いられます。

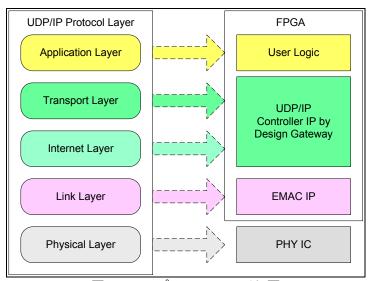

図 1: UDP プロトコルのレイヤ図

UDP1G-IPコアは UDP1G-IPプロトコルにおいてトランスポート層とインターネット層を実装します。送信機能においては、UDP1G-IPコアはユーザ・ロジックからの UDP データを用意し UDP1G-IP ヘッダを付加して EMAC を通して送信するイーサネット・パケットを生成します。 受信機能においては、UDP1G-IP コアはイーサネット・パケットから UDP データを抽出します。 このとき UDP1G-IP ヘッダは有効なパケットであるかチェックされます。 パケットが有効であった場合 UDP データが抽出されユーザ・ロジックから読み出せるようデータ・バッファに格納されます。 より低いプロトコル層はIntelのEMAC-IPと外付けPHYチップで実装します。

本リファレンス・デザインは簡単なユーザ・ロジックで接続した UDP1G-IP コアを使ってデータの送信・受信を評価するシステムを提供します。 本システムは Intel 製各種評価ボードおよびテスト・アプリケーションを搭載したテスト PC で高い転送パフォーマンスが得られることを検証します。より詳細については以下で説明します。

# 2. デザインの動作環境

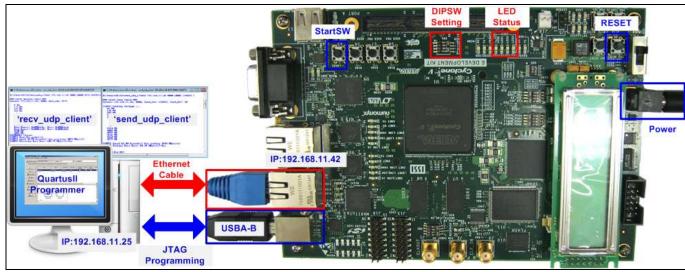

このリファレンス・デザインは下図2に示すような以下の環境で動作するデザインです。

- Intel 製 FPGA 評価ボード

- QuartusII プログラマ

- イーサネット・ケーブル(カテゴリ 5e または 6)

- ギガビット・イーサネットのポートを持つパソコン

- JTAG で FPGA をコンフィグレーションする評価ボード付属の USB ケーブル

- DesignGatway 社から提供される PC 側で動作する"send\_udp\_client" および "recv\_udp\_client"テスト・アプリケーション

図2リファレンス・デザインの動作環境

## 3. ハードウエアの説明

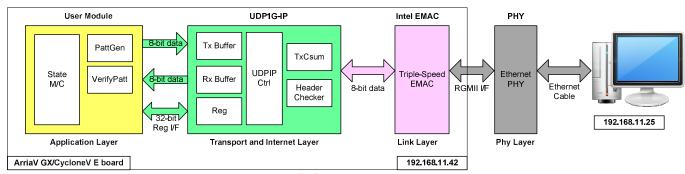

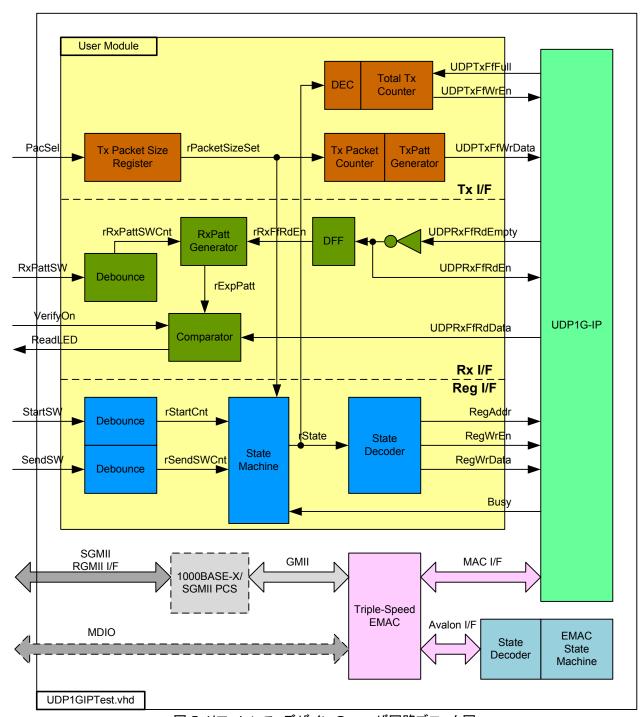

図 3:RGMII I/F によるリファレンス・デザイン(CycloneV E/ArriaV GX)のハードウエア構成

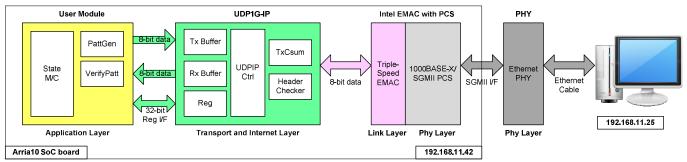

図 4:SGMII I/F によるリファレンス・デザイン(Arria10 SoC)のハードウエア構成

図3または図4に示すようにハードウエア全体は大きく4つのモジュールに分かれており、UDP各々のプロトコル層をサポートします。UDP1G-IPコアはEMACおよび外部PHYとあわせてUDPプロトコルの低層を実装します。本リファレンス・デザインはPC上で動作する2種類のテスト・アプリケーションを同時に起動することで送受信両方向のデータ転送が実行できます。

FPGA から PC への送信方向において UDP データはユーザ・モジュール内のパターン発生器で生成されます。 PC 側では受信したデータをテスト・アプリケーション(recv\_udp\_client.exe)内でベリファイします。 PC から FPGA への受信方向において PC 上のテスト・アプリケーション(send\_udp\_client.exe)にて生成し FPGA が受信したデータはユーザ・モジュール内でベリファイします。 UDP1G-IP コアへのコマンド発行やステータス確認は 32 ビットのレジスタ・インターフェイスを介してステート・マシンで実装しています。 UDP1G-IP コアとユーザ回路のデータ・インターフェイスは送受信どちらの方向も8ビットの FIFO で実装されます。

#### ● 外部 PHY

物理レイヤは外付けの PHY チップで実装されます。 PHY チップ間のインターフェイスは 3 種類あります、すなわち SGMII(Arria10SoC ボードの場合)、 RGMII(ArriaV GX スタータ/CycloneV E ボードの場合)、 GMII です。

#### EMAC

リンク層と PCS/PMA モジュールは Intel 社から提供されるトリプル・スピード・イーサネット MAC で実装されます。 EMAC は2種類のユーザ・インターフェイスがあり、ひとつはデータ転送の Avalon ストリームでもうひとつはコンフィグレーション用の Avalon-MM です。本デモ・システムでは EMAC の Avalon ストリームは UDP1G-IP コアと直結しますが Avalon-MM インターフェイスは EMAC をコンフィグレーションする EMACCtrl モジュールと接続されます。 EMACCtrl モジュールはステート・マシンを内蔵し EMAC および外部 PHY の基本的な初期化を行うため起動後1度のみ実行します。 EMAC のレジスタ詳細については以下 Intel 社提供のドキュメント"Triple-Speed Ethernet MegaCore Function User Guide"の"Configuration Register Space"の章を参照してください。 https://www.altera.com/en US/pdfs/literature/ug/ug ethernet.pdf

EMAC ステート・マシンの動作シーケンスは SGMII とRGMII で異なります。 SGMII モードの場合、EMAC ステート・マシンはベース・コンフィグレーション空間のみアクセスし MAC 機能のコンフィグレーションにて送信および受信パスの禁止/許可設定、フレーム長、送信 IPG 長、ソフトウエア・リセットなどを実行します。

一方 RGMII モードの場合、EMAC ステート・マシンはベース・コンフィグレーション空間と MDIO 空間 1 の両方をアクセスします。MDIO 空間 1 は MDIO インターフェイスを通して外部 PHY の内部レジスタをアクセスするために使われ、RGMII 受信/送信タイミング制御機能をイネーブルとします。 タイミング制御ビットがイネーブルされると送信および受信クロックは送信データ/受信データとの同期を取るためクロック位相シフトのディレイを設定できます。

#### UDP1G-IP

UDP1G-IP コアの詳細や I/O 信号、タイミング波形、レジスタマップについては、UDP1G-IP コア データシート ("dg\_udpip\_data\_sheet\_intel\_jp.pdf")を参照してください。

### ● ユーザ回路

図 5: リファレンス・デザインのユーザ回路ブロック図

ユーザ回路は大きく3つのブロックに分かれており、それらは送信 FIFO インターフェイス、受信 FIFO インターフェイス、およびレジスタ制御インターフェイスです。

### 送信インターフェイス

送信時の動作としては、送信パターン発生器(TxPattGenerator)が32ビットのインクリメンタル・テスト・パターンを送信 FIFO に向けて出力します。パターンは送信パケット完了ごとにインクリメントされ、また送信パケット・カウンタが各送信パケット内のデータ数をカウントします。 DIP スイッチで2種類のパケット・サイズを選択できますが、、それは1472 バイトの非ジャンボ・フレームと8972 バイトのジャンボ・フレームです。テストパターンは総転送サイズ分の送信が完了するまで発生します。 デザイン内部のステート・マシンにより、ユーザからの新しい転送要求に従います。 総送信カウンタはテスト・データ総数をカウントしますが、本リファレンス・デザインにて総送信数は0xFFFF FFFF(4GB)に固定されています。

### 受信インターフェイス

32 ビットのインクリメンタル・データは受信パターン発生器(RxPattGenerator)でも生成され、UDP1G-IPコアの受信 FIFO インターフェイスからの受信データと比較します。 また、受信 FIFO からのエンプティ・フラグをモニタしデータを FIFO からリードするロジックも実装されています。そしてリード・データが比較元のインクリメンタル・データと不一致を検出すると ReadLED が点滅します。

#### レジスタ・インターフェイス

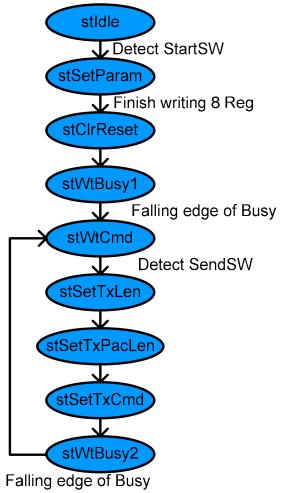

制御インターフェイスはステート・マシンを使ってデザインされています。レジスタ・アドレスと書き込み値はステート・マシンに予め設定されたパラメータで決定され、初期化プロセスや送信動作におけるパケット・サイズや転送数と合わせてレジスタにセットするよう制御されます。送信動作はユーザによる SendSW 押下で開始します。ステート・マシンの状態遷移図を図 6 に示します。IPコアからの Busy フラグは IPコアの動作が完了したことを検出するためにモニタされます。

図 6: ユーザ回路内ステート・マシンの状態遷移図

ステート・マシンはユーザにより StartSW ボタンが押下されると stSetParam ステートに遷移します。 そのステートにて UDP1G-IP コアに対してレジスタを介して以下のパラメータをセットします。

- Source MAC address = 00:01:02:03:04:05 - Source IP address = 192.168.11.42

- Source Port number = 4000

- Destination IP address = 192.168.11.25

Destination Port number for Tx(DPN Reg[15:0]) = 60000

Destination Port number for Rx(DPN Reg[31:16]) = 60001

その後次のステートとなる stClrReset に遷移し UDP1G-IP コアへのリセット信号を解除(RST レジスタ=0)します、すると UDP1G-IP コア内部でパラメータの初期化が実行されます。 ステート・マシンはコアの Busy フラグ立下りエッジをモニタしコア内部の初期化完了を待ちます。 その後 stWtOpen ステートにて接続相手の PC でテスト・アプリケーションの動作開始を待ちます。

データ送信においてステート・マシンは FPGA から PC へ 4GByte のテスト・データを送信するデザインとなります。 ユーザが SendSW ボタンを押下すると、ステート・マシンは stSetTxLen ステートに遷移し総転送サイズ(TDL レジスタ)をセット、stSetTxPacLen ステートに遷移しパケット・サイズ(PKL レジスタ)をセットして最後に stSetTxCmd ステートに遷移し送信開始(CMD レジスタ)をセットします。 そして stWtBusy2 ステートにて Busy 信号をモニタし転送完了を 待ちます。 全データの送信が完了したら stWtCmd ステートに戻り次のコマンドを待機します。

データ受信において、本 IP コアは PC からの UDP データを特にステート・マシンによるレジスタの設定なしでユーザ・ロジックに転送できます。従ってユーザは送受信の両方の転送を同時に実行することが可能です。

## 4. PC 側テスト・アプリケーション

本リファレンス・デザインの実機動作を検証するため、接続相手の PC 側にて"recv\_udp\_client"および "send\_udp\_client"の2種類のテスト・アプリケーションが提供されています。 両方のアプリケーションを同時に実行可能とするため、PC 側のポート番号は異なる番号が使われます。 FPGA から PC への転送(recv\_udp\_client)ではポート番号 60000 であり、PC から FPGA への転送(send\_udp\_client)ではポート番号 60001 を使います。どちらのアプリケーションも DOS ベースのプログラムですので、送受信を同時に実行する場合 2 つの DOS 窓を開いてそれぞれのテスト・アプリケーションを実行する必要があります。 送受信同時テストの場合、recv\_udp\_clientによる PC 側の受信においてはネットワーク負荷による受信パケットのドロップ(ロスト)が発生しやすくなるのでご注意ください。

#### recv udp client

このテスト・アプリケーションは UDP1G-IP コアの送信機能を検証するためのソフトウエアであり、PC が受信するデータをベリファイします。 本アプリケーションはコマンド発行時に以下に示すパラメータ引数を入力しますが、それは FPGA 内ユーザ回路の HDL コードで固定された値と一致させる必要があります。コマンドの引数を変更したい場合、リファレンス・デザインのユーザ・ロジックの HDL コードを変更させる必要があります。

Dst Addr: FPGA 側の IP アドレス、"192.168.11.42"と設定する必要があります

Dst\_Port: FPGA 側のポート番号、"4000"と設定する必要があります

Src Port: PC 側のポート番号、"60000"と設定する必要があります

Recv\_Len: バイト数単位でのパケット・サイズ、非ジャンボ・フレームでは "1472"、ジャンボ・フレームでは"8972" と設定する必要があります。この値を正しく設定しない場合、テスト・アプリケーションにベリファイ・エラーが表示され動作は停止します。

Total Len: バイト数単位での総転送数、"4294967295" と設定する必要があります

このテスト・アプリケーションの動作シーケンスは以下です。

- (1) ユーザのコマンドラインからパラメータを取得します。

- (2) ソケットを作成し受信バッファのプロパティをセットします。

- (3) ユーザ指定パラメータより IP アドレスとポート番号をセットし接続します。

- (4) データの受信とベリファイ比較を総転送数かあるいは 0.5 秒以内にそれ以上データ受信がなくなるまで繰り返します。比較データは各パケット・サイズ (1472 バイトあるいは 8972 バイト) 毎にインクリメントする 32 ビットの値です。よって同一のパケット内の全データは同一値となります。このベリファイ時に以下に示す2種類のエラーを検出すると画面に表示します。

- "Drop Expect": パケットの先頭データが期待値でなかった場合に表示されます、これはワーニング・メッセージでアプリケーションはデータのベリファイは継続します。

- "Error Expect": パケット内のデータが先頭データと一致しなかった場合に表示されます、これはエラー状態なのでアプリケーションは動作を停止させます。

- プログラム実行中アプリケーションは毎秒ごとに総受信サイズを表示します。

- (5) a) PC からソケットをクローズします。アプリケーションは受信データ数から転送パフォーマンスとドロップしたパケット数を表示します。

- b) UDP 転送ではしばしばパケットのロストが発生します、このためテスト・アプリケーションは 0.5 秒のタイム アウトが設定されています。 0.5 秒間にデータを受信しなかった場合、テスト・アプリケーションはデータ転送 のループ処理を終了しソケットをクローズします。この場合、"Timeout"のメッセージが表示されアプリケーションは設定された数以下のデータしか受信されなかったことを示します。

### send\_udp\_client

このテスト・アプリケーションは UDP1G-IP コアの受信機能を検証するためのソフトウエアです。recv\_udp\_client と 同様ユーザはコマンドラインで以下に示す各パラメータを設定しますが FPGA 内ユーザ回路の HDL コードで固定された値と一致させる必要があります。 コマンドの引数を変更したい場合、リファレンス・デザインのユーザ・ロジックの HDL コードを変更させる必要があります。

Dst Addr: FPGA 側の IP アドレス、"192.168.11.42"と設定する必要があります

Dst Port: FPGA 側のポート番号、"4000"と設定する必要があります

Src\_Port: PC 側のポート番号、"60001"と設定する必要があります recv\_udp\_clientと同時並列して実行できるよう、 異なるポート番号を使います。

Packet Count: PC から FPGA へ送信する 8K バイト・パケットの総パケット数を指定します。従って総データ数はこの設定数 x8096 バイトとなります。有効な設定値は 1-524287 です。

Verification On/Off: '0'にセットすると送信するデータはオール・ゼロのダミー・データとなり、'1'をセットすると 32 ビットのインクリメンタル・データとなります。この値は PC からのデータ送信パフォーマンスに影響します。 PC によっては'0'をセットするダミー・データの方が'1'によるインクリメンタル・データよりパフォーマンスが良好な場合があります。

このテスト・アプリケーションの動作シーケンスは以下です。

- (1) ユーザのコマンドラインからパラメータを取得します。

- (2) ソケットを作成し送信バッファのプロパティをセットします。

- (3) ユーザ指定パラメータより IP アドレスとポート番号をセットし接続します。

- (4) 送信バッファにダミー・データ(オール 0)またはインクリメンタル・データを準備し送信を開始します。 各パケット・サイズは 8096 バイト固定です。 このパケット・サイズを使うことでジャンボ・フレームをサポートする PC で UDP パケットをフラグメントなしで生成することが可能となります。

- 注意: UDP1G-IP コアはフラグメントされた IP パケットの受信をサポートしません。

- (5) ソケットをクローズしテスト結果として転送パフォーマンスを表示します。

# 5. 改版履歴

| リビジョン | 日付        | 履歴              |

|-------|-----------|-----------------|

| 1.0   | 6-Jan-16  | Initial Release |

| 1.0J  | 2017/3/21 | 日本語版第1版作成       |

Copyright: 2016 Design Gateway Co,Ltd.