## **UDP10G-IP Core**

2017/11/13 データシート Rev1.0J

## **Design Gateway Co.,Ltd**

● 本社: 〒184-0012

東京都小金井市中町 3-23-17

電話/FAX: 050-3588-7915

E-mail: sales@dgway.com

URL: www.dgway.com

## 特長

- UDP/IP プロトコル・スタックを実装

- IPv4 に対応

- 単一ポート接続

(コアを複数インスタンスすることでマルチ・セッションに対応可)

- 8 バイト(64 ビット)単位での送受信パケット・サイズに対応

- 送受信バッファはリソースとパフォーマンスに合わせて最適化調整が可能

- データは標準的な FIFO 接続

- 制御は一般的なレジスタ・インターフェイス接続

- Intel 標準 10-Gbps イーサネット MAC コアと接続する 64 ビット Avalon ストリーム・インターフェイス

- クロック周波数 156.25MHz の単一クロック・ドメイン

- Arria10GX 評価ボードで実機動作するリファレンス・デザインを提供

- IP フラグメントに対応

- 安心の国内サポート

#### 表 1: コンパイル結果例

| Family     | Example Device | Fmax<br>(MHz) | ALMs  | Registers <sup>1</sup> | Pin | Block<br>Memory bit <sup>2</sup> | Design<br>Tools |

|------------|----------------|---------------|-------|------------------------|-----|----------------------------------|-----------------|

| Arria10 GX | 10AX115S2F45I1 | 156.25        | 1,327 | 1,979                  | -   | 1,179,648                        | QuartusII 16.0  |

#### 備考:

- 1)実際のリソース消費カウントはユーザロジックやフィット条件等に依存します。

- 2)ブロックメモリの消費リソース数は送信データ・バッファ 64K バイト、送信パケットバッファ 16K バイト、受信データバッファ 16K バイト (ジャンボフレーム対応)です。

| Core Facts            |                         |  |  |  |  |

|-----------------------|-------------------------|--|--|--|--|

| コアの提供情報               |                         |  |  |  |  |

| 提供ドキュメント              | ●データ・シート                |  |  |  |  |

|                       | ●リファレンス・デザイン説明書         |  |  |  |  |

|                       | ●実機デモ手順書                |  |  |  |  |

| コア形態                  | ●暗号化されたネットリスト           |  |  |  |  |

| 検証方法                  | ●参照デザインによる実機評価          |  |  |  |  |

| 制約ファイル                | ●参照デザインで SCF ファイル       |  |  |  |  |

| デザイン例使用言語             | ●VHDL                   |  |  |  |  |

| その他                   | ● Arria 10GX ボード用参照デザイン |  |  |  |  |

| シミュレーション環境            |                         |  |  |  |  |

| ModelSim-Altera 10.1e |                         |  |  |  |  |

|                       | 技術サポート                  |  |  |  |  |

| デザイン・ゲートウェイによる日本語サポート |                         |  |  |  |  |

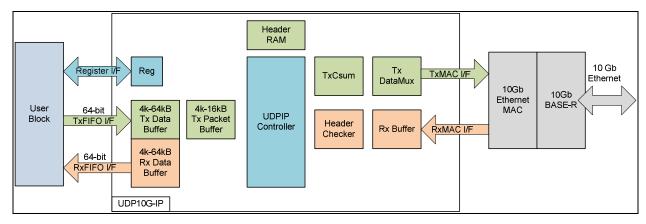

図1: UDP10G-IP コア内部ブロック図

## アプリケーション情報

UDP10G-IP コア(以下本 IP コア)は動画データ・ストリーミングのような UDP/IP プロトコルを使ったネットワーク・アプリケーションにおいて高速でのデータ転送を可能とする機能を提供します。 本コアを使うことで、ユーザは CPU を使わずにハードワイヤード・ロジックのみで UDP/IP プロトコルによるデータ転送を可能とします。

## コア概要

本 IP コアは Intel 社から提供される 10GbE EMAC IP コアおよび 10GbE BASE-R PHY と合わせてることで、 UDP/IP スタック、トランスポート層、インターネット層、リンク層、そしてネットワーク・データ転送の物理層として機能します。本 IP コアを使ったシステムにより、UDP/IP プロトコルにてネットワークの外部デバイスとデータ転送を実行できます。

本 IP コアは 3 種類のユーザ・インターフェイスがあり、一つは制御用レジスタ・アクセスのインターフェイスで、他の 二つは送信と受信の FIFO インターフェイスです。システムの初期化時に、ユーザはパケット・サイズ、ポート番号、IP 番号等をレジスタ・インターフェイスを介して設定する必要があります。そしてコマンド指示により送信データ・バッファから外部ネットワーク・デバイスへのデータ送信を実行します。また、外部デバイスからの受信データは受信パケットの UDP ヘッダが有効であった場合、UDP データのみを抽出し本 IP コアの受信データ・バッファに格納します。

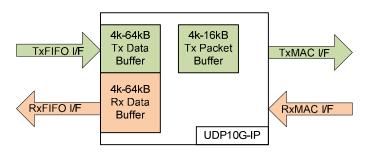

図 2: 送信/受信バッファのサイズは調整可能

本 IP コアの 3 種類のバッファ(送信データ・バッファ、送信パケット・バッファ、受信データ・バッファ)は IP コアのパラメタライズで設定が可能です。ブロック RAM 消費リソースとパフォーマンスをユーザ・アプリケーションに対して最適化できます。送信データ・バッファと送信パケット・バッファのサイズは、レジスタ・インターフェイスを介して設定可能な送信パケットのサイズに関係します。送信パケット・バッファの容量は必ず送信パケット・サイズよりも大きく設定する必要があり、送信データ・バッファは送信パケット・バッファより少なくとも 2 倍のサイズとする必要があります。

また、パケットの受信とユーザ回路への受信データ転送を同時に行えるようにするため、受信データ・バッファは受信パケット・サイズの2倍以上に設定する必要があります。

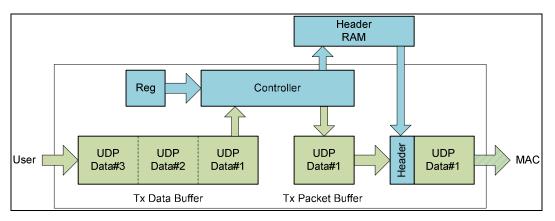

図 3: 送信のデータ・フロー

データの送信時は、送信データ・バッファからのデータはパケット・サイズに分割され送信パケット・バッファに転送されます。レジスタで設定されたパラメータはパケットのヘッダ作成に使われヘッダ RAM 内に格納されます。送信パケット・バッファからの送信データは MAC へ出力される前にコア内部にてヘッダ RAM のヘッダ・データと結合し UDP パケットが生成されます。UDP チェックサムおよび IP チェックサムはコア内で自動計算されます。レジスタ内のビジー・フラグはユーザによって予め設定された転送サイズ分のデータ転送が完了するとクリアされます。ユーザ回路はこのビジー・フラグをモニタすることで転送状態が把握できます。UDP10G-IPコアがアイドル状態に復帰した後ユーザは送信パケット・サイズや総転送長を変更できます。

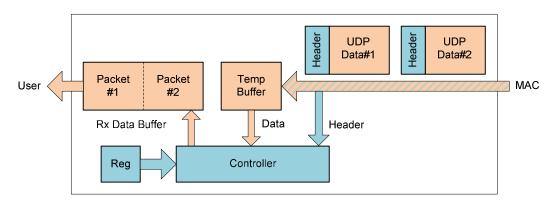

図 4: 受信のデータ・フロー

データの受信時には受信パケットはまずテンポラリ・バッファに一旦格納されます。そして受信パケット内のヘッダとチェックサムが精査され、ヘッダ内容やチェックサムにエラーがあった場合はそのパケットは破棄されるので受信データ・バッファには格納されません。従って有効なデータのみが選別され受信データ・バッファに格納されることになります。

## コアの機能ブロック

本 IPコアは、制御ブロック、送信ブロック、受信ブロックの3ブロックに分かれています。

## 制御ブロック

#### • レジスタ

ユーザ回路は UDP/IP オペレーションに関するパラメータをレジスタ・インタフェースにより設定できます。 レジスタ・アドレスは全4ビットです。それぞれのレジスタのアドレス・マッピングを表2に示します。 RST レジスタによるリセットが解除されると、各パラメータを設定したレジスタを初期値として動作が開始されます。

#### • UDPIP コントローラ

リセットが解除されると IP コアは ARP 要求を送信し ARP 応答情報から通信ターゲットの MAC アドレスを取得します、その後コアはユーザからの外部デバイスへのデータ転送開始指示を待ちます。

#### 表 2: レジスタ・マップ

| アドレス  | レジ      | 方         | ビット    | 説明                                                                                                                                                                                                                           |

|-------|---------|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [3:0] | スタ<br>名 | 向         |        |                                                                                                                                                                                                                              |

| 0000b | RST     | Wr<br>/Rd | [0]    | 本 IP コアのリセット。'1'でリセットし'0'でリセットを解除する。 初期状態は'1'(リセット状態)で、ユーザ回路が動作に必要な全パラメータをレジスタにセットしてから本レジスタに'0'を書き込むことでコアの動作が開始する。 ユーザ回路が SML, SMH, DIP, SIP, DPN, SPN レジスタの値を変更する必要が生じた場合、本レジスタを一旦'1'としコアをリセット状態に移行させてから変更しなくてはならない。        |

| 0001b | CMD     | Wr        | [0]    | '1'でデータ送信開始<br>本レジスタによってデータ送信を指示する前に、ユーザ回路は Busy 信号または本レジ<br>スタの bit[0]をリードしチェックしてコアが動作中でないことを確認しなくてはならない。                                                                                                                   |

|       |         | Rd        | [0]    | システム・ビジー・フラグ。 '0': アイドル状態、'1': ビジー状態、Busy 出力信号と同一                                                                                                                                                                            |

| 0010b | SML     | Wr<br>/Rd | [31:0] | コアの MAC アドレスの下位 32bit 定義レジスタ。RST レジスタをクリアする前に本レジスタで MAC アドレスを指定する必要がある。                                                                                                                                                      |

| 0011b | SMH     | Wr<br>/Rd | [15:0] | コアの MAC アドレスの上位 16bit 定義レジスタ。RST レジスタをクリアする前に本レジスタで MAC アドレスを指定する必要がある。                                                                                                                                                      |

| 0100b | DIP     | Wr<br>/Rd | [31:0] | ターゲット側の IP アドレス 32bit を指定する。 RST レジスタをクリアする前に本レジスタ で IP アドレスを指定する必要がある。                                                                                                                                                      |

| 0101b | SIP     | Wr<br>/Rd | [31:0] | 本システム側の IP アドレス 32bit を指定する。 RST レジスタをクリアする前に本レジスタで IP アドレスを指定する必要がある。                                                                                                                                                       |

| 0110b | DPN     | Wr<br>/Rd | [31:0] | [15:0] IPコアからの送信にて送信先ターゲット側のポート番号を 16bit で指定する。 [31:16] IPコアへの受信にて受信元ターゲット側のポート番号を 16bit で指定する。 RSTレジスタをクリアする前に本レジスタでポート番号を指定する必要がある。                                                                                        |

| 0111b | SPN     | Wr<br>/Rd | [15:0] | 本システム側のポート番号を 16bit で指定する。RST レジスタをクリアする前に本レジスタで自身のポート番号を指定する必要がある。                                                                                                                                                          |

| 1000b | TDL     | Wr        | [31:0] | 送信データ数を8の倍数バイト単位で指定する。 有効な値は8~0xFFFFFF8(下位2ビットは無視される)。 CMD レジスタで送信開始を指示する前に本レジスタで送信データ数をセットする必要がある。 ユーザが本レジスタでセットした送信データ数はコア内部ロジックでラッチされるため、現在送信中であっても、次の送信のデータ数をセットしておくことが可能である。また、次の送信でも再度同じ送信データ数である場合は本レジスタに再セットする必要はない。 |

|       |         | Rd        | [31:0] | まだ送信されていない残りデータ数をバイト単位で表示する。                                                                                                                                                                                                 |

2017/11/13

# 表 2: レジスタ・マップ(続き)

|               |        | 7 7 (496) |        |                                                                                                                                                                                                                             |

|---------------|--------|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| アドレス<br>[3:0] | レジスタ 名 | 方向        | ビット    | 説明                                                                                                                                                                                                                          |

| 1001b         | ТМО    | Wr        | [31:0] | 全てのコマンドにて、受信パケットの待ち時間タイムアウト値を設定する。 本レジスタは 156.25MHz のカウンタで動作するためタイマ設定値は 6.4ns の単位で指定する。 本 レジスタ値は 0x6000 以上の値としなくてはならない。                                                                                                     |

|               |        | Rd        |        | 各タイムアウト等のステータス、それぞれのビット定義は以下の通り [0] ARP で返信パケットをタイムアウト時間内に受信しなかった、タイムアウト後本 IPコアは ARP 応答を受信するまで ARP 要求を繰り返す [8] 受信データ・バッファが一杯のため受信パケットを受け損ねた [9] 受信パケットのチェックサムが間違えていたため受信パケットを破棄した [10] MacRxUser エラーが検出されたため受信パケットを破棄した     |

| 1010b         | PKL    | Wr<br>/Rd | [15:0] | 8の倍数バイト単位で指定する送信パケットのデータ長。8~16000の範囲で指定する必要がある(下位 2 ビットは無視される)。 デフォルト値は 1472 バイト(非ジャンボ・フレームの最大サイズ) この値はデータ転送(Busy フラグ=1)中に変更してはならない。次の転送でも同じパケット・サイズの場合、コア内部で前の値は保持されているのでユーザ回路は本レジスタを再度セットする必要はない。                         |

| 1110b         | SRV    | Wr/R<br>d | [0]    | '0': クライアント・モード、本 IP コアはリセット解除後 ARP 要求を接続相手に向けて送信し、MAC アドレスを取得する、相手からの ARP 応答を受信するとコアの Busy はネゲートする。 '1': サーバー・モード、本 IP コアはリセット解除後相手からの ARP 要求を待機する、ARP 要求を受信し ARP 応答を送信した後にコアの Busy はネゲートする。このレジスタの初期値は'0'(クライアント・モード)である。 |

| 表 3: 各バッファ(TxBuf/TxPac/RxBufBitWidth)の容量/ | ▮パラメータ |

|-------------------------------------------|--------|

|-------------------------------------------|--------|

| 有効なビット幅 | バッファ容量  | 送信データ・バッ | 送信パケット・バッ | 受信データ・バッ |

|---------|---------|----------|-----------|----------|

|         |         | ファ有効ビット幅 | ファ有効ビット幅  | ファ有効ビット幅 |

| 9       | 4kByte  | Valid    | Valid     | Valid    |

| 10      | 8kByte  | Valid    | Valid     | Valid    |

| 11      | 16kByte | Valid    | Valid     | Valid    |

| 12      | 32kByte | Valid    | No        | Valid    |

| 13      | 64kByte | Valid    | No        | Valid    |

#### 送信ブロック

#### • 送信データ・バッファ (Tx Data Buffer)

このデータ・バッファの容量は本 IP コアの"TxBufBitWidth"パラメータで指定します。有効な値の範囲は表 3 に 示すように 9(4K バイト)~13(64K バイト)で 64 ビット幅バッファのアドレス・サイズに該当します。 このバッファ・サイズは表 3 の PKL レジスタで設定する送信パケット・サイズの少なくとも 2 倍かそれ以上のサイズとする必要があります。送信時は本送信データ・バッファから送信パケット・バッファへ 1 パケット分のデータを 転送するのと同時にユーザ回路から次のパケット用のデータを受信します。MAC へパケットが出力されると本バッファ内のデータはフラッシュされます。このため現在パケットの送信と次パケットの準備を同時に並行して行うためにパケット・サイズの 2 倍の容量が必要です。このバッファ・サイズを 2 倍より大きくすることによりコア内での ユーザ回路からのデータ・フロー制御に貢献します。バッファ内に多数のデータを貯めることで本 IP コアからの データ送信中にユーザ回路は他の処理を実行できます。

#### 送信パケット・バッファ (Tx Packet Buffer)

このバッファの容量は本 IP コアの"TxPacBitWidth"パラメータで指定します。 有効な値の範囲は表 3 に示すように 9(4K バイト)~11(16K バイト)です。このバッファ・サイズは PKL レジスタで設定する送信パケット・サイズと同じかそれ以上とする必要があり、送信データ・バッファからの 1 パケット分のデータを格納します。送信パケット・バッファ内のデータは MAC のデータ受信準備が完了するまで保持されます。MAC が長時間データ受信レディとならない場合本バッファは最大 2 データ・パケット分のデータを保持します。このため本バッファにて 2 パケット分以上の残りスペースは使われません。

#### • ヘッダ RAM (Header RAM)

この RAM には送信パケットのヘッダ部を格納します。 ユーザ回路から RST レジスタによるリセット解除でヘッダ RAM 内のパラメータは更新されます。 いくつかのパラメータ例えばターゲット MAC アドレスは ARP 応答(クライアント・モード)/ARP 要求(サーバー・モード)によって更新されます。

## • 送信チェックサム (TxCsum)

送信パケットが送出される前に本モジュールによりチェックサムが計算されます

#### • 送信データ・マルチプレクサ (TxDataMux)

本モジュールによりヘッダ RAM と送信データ・バッファ内のデータが結合されイーサネット MAC を介して外部に送出されます。

#### 受信ブロック

### • 受信バッファ (Rx Buffer)

このバッファはヘッダ・チェッカで処理される前のイーサネット MAC からの全ての受信パケットを一時的に保持します。

#### • ヘッダ・チェッカ (Header Checker)

受信パケット内のヘッダをチェックしユーザ回路からの設定値と比較します。 ヘッダの内容が設定パラメータと適合しなかった場合やチェックサムがエラーであった場合は該当するパケットは破棄されます。 ただし IP フラグメントされたパケットの場合 UDP チェックサムは検証されません。チェックサムが適合した場合、UDP データのみが分離され受信データ・バッファに転送されます。

### • 受信データ・バッファ (Rx Data Buffer)

このバッファの容量は本 IPコアの"RxBufBitWidth"パラメータで指定します。 有効な値の範囲は表 3 に示すように 9(4K バイト)~13(64K バイト)です。このバッファはユーザ・ロジックと本 IPコア間に配置されます。このバッファが一杯の場合、新たに受信したパケットは無視(ロスト)します。このため、新たなパケット受信と前パケットのユーザ回路への転送を同時に実行する場合、少なくとも受信パケット・サイズの 2 倍の容量が必要です。

## ユーザ回路

ユーザ回路はレジスタ I/F を通してパラメータの設定やコア状態のモニタを行い、また、送信 FIFO I/F を介した送信データの書き込みや受信 FIFO I/F を介して受信データの読み出しを行います。 ユーザ回路はシンプルなハードウエア・ロジックで実装できるので、NiosII などのプロセッサを使わずにシステムを構築することが可能です。

### 10Gb イーサネット MAC コアおよび 10Gb BASE-R

このモジュールは Intel 社から提供される IPコアです。詳細については以下の Intel 社サイトを参照してください。 <a href="https://www.altera.com/products/intellectual-property/ip/interface-protocols/m-alt-10gbps-ethernet-mac.html">https://www.altera.com/products/intellectual-property/ip/interface-protocols/m-alt-10gbps-ethernet-mac.html</a> https://www.altera.com/products/intellectual-property/ip/interface-protocols/m-alt-10gbase-r-pcs.html

## コアの I/O 信号

コアのパラメータを表 4 に、全 I/O 信号を表 5 で説明します。 MAC インターフェイスは Intel 製 10Gb EMAC コアの Avalon ストリーム・インターフェイスと直結できます。

## 表 4: コアのパラメータ

| ジェネリック名       | 設定範囲 | 説明                                   |

|---------------|------|--------------------------------------|

| TxBufBitWidth | 9-13 | 送信データ・バッファ・サイズを 64 ビット幅のデータ・インターフェイ  |

|               |      | スにおけるアドレス・ビット幅で設定します。                |

| TxPacBitWidth | 9-11 | 送信パケット・バッファ・サイズを 64 ビット幅のデータ・インターフェイ |

|               |      | スにおけるアドレス・ビット幅で設定します。                |

| RxBufBitWidth | 9-13 | 受信データ・バッファ・サイズを 64 ビット幅のデータ・インターフェイ  |

|               |      | スにおけるアドレス・ビット幅で設定します。                |

## 表 5: コアの I/O 信号

| 信号名                   | 方向  | 説明                                                     |  |

|-----------------------|-----|--------------------------------------------------------|--|

| 1874                  | 1-3 | 共通 I/F 信号                                              |  |

| RstB                  | In  | IP コアのリセット: ロウ・アクティブ信号である。                             |  |

| Clk                   | In  | 物理(PHY)層から出力される 156.25MHz のシステム・クロック                   |  |

|                       |     | ユーザ I/F                                                |  |

| RegAddr[3:0]          | In  | レジスタの 4bit アドレスバス                                      |  |

| RegWrData[31:0]       | In  | ライト・レジスタの 32bit 書込みデータ・バス                              |  |

| RegWrEn               | In  | レジスタのライト・イネーブル、アドレスおよびデータに有効な値をセットし本信号にパルスを与え          |  |

|                       |     | ることで書込みを実行する。                                          |  |

| RegRdData[31:0]       | Out | レジスタの 32bit 読み出しデータ・バス、レジスタアドレスをセットしてから1クロックのレイテンシ     |  |

|                       |     | 後に有効なリード・データが本バス上に現れる。                                 |  |

| Busy                  | Out | コアのビジー状態('0':アイドル状態、'1'コアは初期化中またはビジー状態。                |  |

| IntOut                | Out | タイムアウト発生または受信パケットの破棄時に本信号が 1 クロック期間分 H アサートされる。        |  |

|                       |     | ユーザ回路は TMO レジスタで割り込み要因を確認することができる。                     |  |

|                       |     | 送信データ・バッファ I/F                                         |  |

| UDPTxFfFull           | Out | コアの送信データ・バッファの Full フラグ。ユーザ回路は本信号が H アサートされてから 4 クロ    |  |

|                       |     | ック期間以内に送信データの書込みを停止しなくてはならない。                          |  |

| UDPTxFfWrEn           | In  | 送信データ・バッファのライト・イネーブル。送信データを書き込む際にアサートする。               |  |

| UDPTxFfWrData[63:0]   | In  | 送信データ・バッファの 64bit 書込みデータ・バス、UDPTxFfWrEn に同期する。         |  |

|                       |     | 受信データ・バッファ I/F                                         |  |

| UDPRxFfRdCnt[12:0]    | Out | 受信データ・バッファ内の受信データ総量を 64bit 単位で示す FIFO データ・カウンタ         |  |

| UDPRxFfRastRdCnt[2:0] | Out | 受信データ・バッファ内の最終データでの残留バイト数、0-7 のいずれかの値となる。総受信デ          |  |

|                       |     | ータ・バイト数が8の倍数でない場合はこの値は非ゼロとなる。                          |  |

| UDPRxFfRdEmpty        | Out | 受信データ・バッファの FIFOEmpty フラグ。 ユーザ回路は本信号が Hアサートされたら直ち      |  |

|                       |     | にデータの読み出しを停止しなくてはならない。                                 |  |

| UDPRxFfRdEn           | In  | 受信データ・バッファの読み出しイネーブル。受信データを読み出す際にアサートする。               |  |

| UDPRxFfRdData[7:0]    | Out | 受信データ・バッファの 32bit 読出しデータ・バス、UDPRxFfRdEn をアサートしてから1クロック |  |

|                       |     | 期間のレイテンシ後に有効なリードデータが出力される。                             |  |

## 表 5: コアの I/O 信号(続き)

| 信号名             | 方向  | 説明                                                    |

|-----------------|-----|-------------------------------------------------------|

|                 |     | MAC I/F 信号                                            |

| MacRxData[63:0] | In  | 受信データ・バス                                              |

| MacRxValid      | In  | 受信データ有効信号、MacRxDataに同期する。この信号はパケット受信の先頭から末尾まで連続       |

|                 |     | して'1'アサートされる必要がある。                                    |

| MacRxEOP        | In  | フレームの最終ワードであることを示す制御信号                                |

| MacRxError      | In  | フレームの最終ワードに同期して、フレーム中にエラーがあったことを示すエラー信号               |

|                 |     | '0': 通常のフレーム、'1':エラー・パケット                             |

| MacRxReady      | Out | フレームの最終ワード(MacRxEOP='1')を受信した後に、次のパケット受信を準備するため 1 クロッ |

| ·               |     | ク期間分'0'ネゲートされる。                                       |

| MacTxData[63:0] | Out | 送信データ・バス                                              |

| MacTxEmpty[2:0] | Out | フレームの最終ワードで使われないバイト数を示す。                              |

| MacTxValid      | Out | EMAC への送信データ有効信号、MacTxData に同期する。                     |

| MacTxSOP        | Out | フレームの先頭ワードであることを示す制御信号                                |

| MacTxEOP        | Out | フレームの最終ワードであることを示す制御信号                                |

| MacTxReady      | In  | ハンドシェーク信号。MacTxData が MAC により受領されたことを示す。この信号はパケット送信   |

|                 |     | の先頭から末尾まで連続して'1'アサートされる必要がある。                         |

2017/11/13

## タイミング・チャート

#### IPコアの初期化

ユーザ回路から RST レジスタでリセット状態を解除されると本 IP コアは SRV レジスタの設定値(クライアント・モード またはサーバー・モード)によって 2 種類のモードで初期化を実行します。

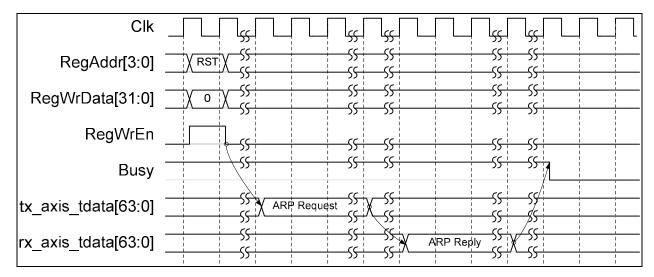

図 5: クライアント・モードでの IP コア初期化

クライアント・モードの場合、本 IP コアは ARP 要求を送信しターゲットからの ARP 応答を待ちます。 ターゲット MAC アドレスは ARP 応答パケットから抽出されます。 その後 Busy 信号は'0'ネゲートされます。

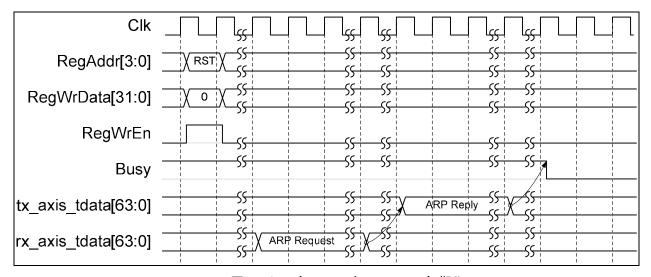

図 6: サーバー・モードでの IP コア初期化

サーバー・モードの場合、本 IPコアはリセット解除後ターゲットからの ARP 要求を待ちます。ターゲットとして設定された値と合致したヘッダを含む ARP 要求を受信すると本 IPコアはターゲットに ARP 応答を送信します。ターゲット MAC アドレスは ARP 要求から抽出します。最後に Busy 信号は'0'ネゲートされます。

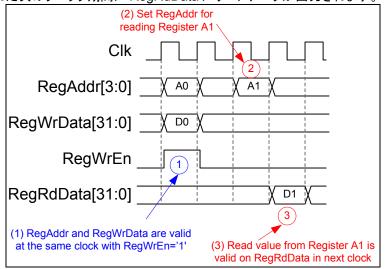

#### レジスタ・インターフェイス

ユーザ回路からの本 IP コア内部へのリードライト・アクセスは図 7 に示すタイミングにより実行します。アクセス先レジスタのアドレスマップは表 3 で示されます。レジスタへの書込みは RegAddr と RegWrData にそれぞれ有効なライト先のアドレスとデータをセットし1クロック期間 RegWrEn='1'とします。レジスタからの読み出しの際は、有効なRegAddr がコアに与えられた次のクロック期間に RegRdData にリードデータが出力されます。

- (1)RegAddr と RegWrData は RegWrEn='1'と同じクロック期間で有効とする必要がある

- (2)読み出し先アドレス A1を RegAddr にセットする

- (3)レジスタ A1 のリード値は次のクロック期間で RegRdData に出力される

図 7: レジスタ I/F のタイミング・チャート

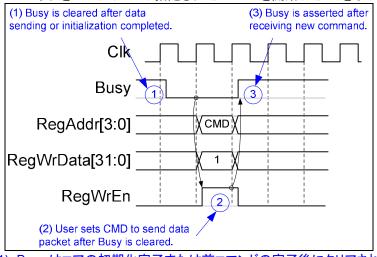

ユーザ回路は CMD レジスタをセットする前にコアの Busy ピンをモニタするかあるいは CMD レジスタの bit0 をリードすることでビジー・フラグがアサートされていないことを確認する必要があります。 CMD レジスタをセットしコマンドを発行すると、図 8 に示すようにコアはビジー・フラグを'1'にアサートし指定されたコマンドを開始したことを示します。

- (1) Busy はコアの初期化完了または前コマンドの完了後にクリアされる

- (2) ユーザ回路は Busy が'0'であることを確認してから CMD レジスタを書き込む

- (3) IPコアがコマンド指示を認識すると Busy をアサートする

図 8: Busy がクリアされた状態からのコマンド発行

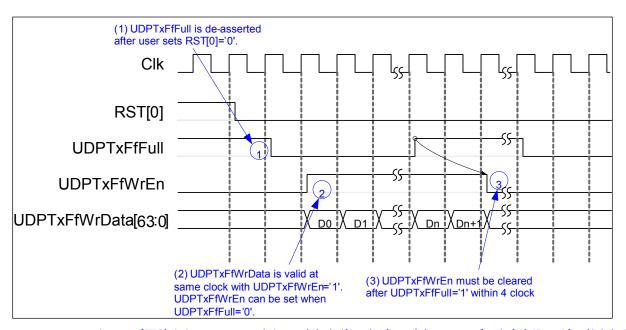

#### 送信 FIFO インターフェイス

ユーザ回路は本 IPコアに対して図 9 に示すように FIFO インターフェイスでデータを送信できます。データを送る前にユーザ回路は FIFO のフル・フラグ (UDPTxFfFull)をチェックしそれが'1'にアサートされていないことを確認する必要があります。そして書き込みデータの UDPTxFfWrData に同期して書き込みイネーブル信号の UDPTx FfWrEn='1'とします。UDPTxFfFull が'1'となった場合、4 クロック以内に UDPTxFfWrEn による書き込み動作を停止しなくてはなりません。また本 IPコアがリセット状態の場合も UDPTxFfFull はアサートされ、FIFO 内の全データはフラッシュされます。

- (1) UDPTxFfFull はユーザ回路から RST[0]='0'とクリアされた後にネゲートされ FIFO データ書き込みが可能となる

- (2) UDPTxFfFull='0'である場合 UDPTxFfWrEn='1'とすることで UDPTxFfWrData を書き込むことができる

- (3) UDPTxFfFull='1'となった場合4クロック以内に UDPTxFfWrEn による書き込み動作を停止しなくてはならない

図 9: 送信データ・バッファ I/F のタイミング・チャート

#### 受信 FIFO インターフェイス

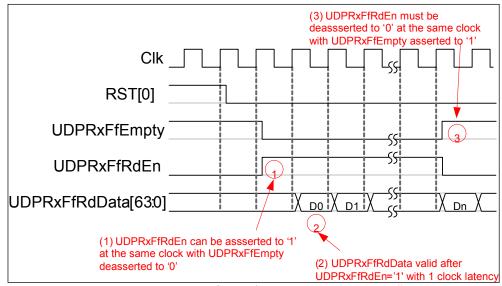

本 IP コアが外部からデータを受信した場合、受信データ・バッファに格納されます。ユーザ回路は図 10 に示すように FIFO インターフェイスでデータを読み出すことができます。ユーザ回路は UDPRxFfEmpty 信号をチェックすることで 受信データの格納状態が把握でき、また UDPRxFfEmpty が'0'でない場合に UDPRxFfRdEn をアサートしてその次 クロック期間に UDPRxFfRdData で受信データを読み出します。UDPRxFfEmpty が'1'となった場合その同一クロック期間内で UDPRxFfRdEn を'0'にネゲートしデータの読み出しを停止しなくてはなりません。送信データ・バッファと 同じように受信データ・バッファも本 IP コアがリセットされると FIFO 内部データをフラッシュします。またコアがリセット中は UDPRxFfEmpty は'1'にアサートされます。

- (1) UDPRxFfRdEn は UDPRxFfEmpty が'0'ネゲートしている同一クロック期間中'1'にアサートできる

- (2) UDPRxFfRdData は UDPRxFfRdEn が'1'アサートされた次のクロック期間に出力される

- (3) UDPRxFfEmpty が'1'にアサートされた場合その同一クロック期間に UDPRxFfRdEn をネゲートする必要がある

図 10: 受信データ・バッファ I/F のエンプティ・フラグについてのタイミング・チャート

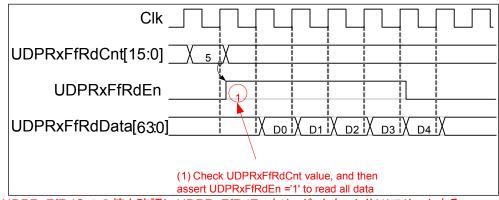

受信データ・バッファの状態は UDPRxFfRdCnt をモニタすることでも確認できます。この信号は受信データ・バッファ に格納されている全データ数を示します。従って図 11 に示すように総受信データ数と同じ期間 UDPRxFfRdEn を'1'にアサートすることで、全受信データを読み出すことができます。

(1) UDPRxFfRdCnt の値を確認し UDPRxFfRdEn をリード・カウント分'1'アサートする

図 11: 受信データ・バッファ I/F のリード・カウンタについてのタイミング・チャート

#### EMAC インターフェイス

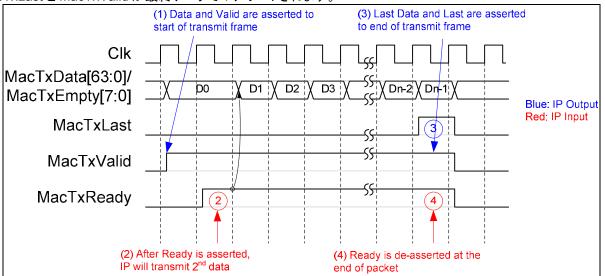

パケットを送信するときに本 IPコアは MacTxValid をアサートし同時に MacTxData 上にパケットの先頭データを出力します。その出力信号はデータ転送要求の応答を示す EMAC からの MacTxReady が'1'アサートされるまで保持します。MacTxReady はパケット転送が完了するまで'1'アサートを継続する必要があります。つまり MacTxValid はパケット最終データまで連続して MacTxData が出力されるよう'1'アサートを維持します。パケットの末尾を示すためMacTxLastと MacTxValid が最終データで'1'アサートされます。

- (1) MacTxData と MacTxValid がアサートされフレームの転送が開始する

- (2) MacTxReady がアサートされると IP コアは 2 番目のデータを出力する

- (3) 送信フレームの最後で MacTxData と MacTxLast がアサートする

- (4) MacTxReady はパケットの末尾でネゲートする

## 図 12: MAC I/F 送信側のタイミング・チャート

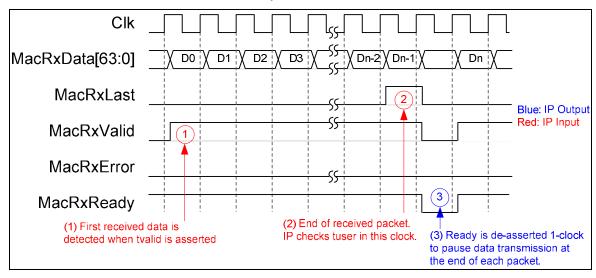

図 13 は受信側のタイミング・チャートです。UDP10G-IPコアは MacRxValid が'0'から'1'アサートする受信フレームの開始をモニタします。MacRxData は MacRxLast がアサートし MacRxError 結果が有効なクロック期間となるパケット末尾まで連続して受信します。MacRxValid はフレーム先頭から末尾まで'1'アサート状態を維持する必要があります。各パケット完了後 1 クロック期間 MacRxReady は'0'ネゲートしデータ転送が一時停止されます。

- (1) MacRxValid がアサートされ受信パケットの先頭データを検出する

- (2) MacRxLast で受信パケットの最後を検出し同時に本 IPコアは MacRxError を評価する

- (3) 各パケット完了後 1 クロック期間 MacRxReady は'0'ネゲートされデータ転送が一時停止する

図 13: MAC I/F 受信側のタイミング・チャート

## コアの制御例

#### クライアント・モード(SRV[0]='0')

クライアント・モードでのデータ送信/受信における本 IP コア内レジスタの設定シーケンス例を以下に示します。

- 1) RST レジスタを'1'にセットし本 IP コアをリセット状態とします。

- 2) SML/SMH レジスタで自身の MAC アドレス、DIP/SIP レジスタで相手/自分の IP アドレス、DPN/SPN レジスタでポート番号を設定します。

- 3) RST レジスタ='0'としてコアのリセット状態を解除します、すると UDP10G-IPコアは通信ターゲットに向けて ARP 要求を送信し ARP 応答から MAC アドレス情報を抽出する初期化を開始します。初期化が完了すると Busi 信号は'0'クリアされその後のユーザ回路からのコマンド発行が可能となります。

- 4) a) データ送信の場合、TDL レジスタに総転送数(8 の倍数で設定)、PKL にパケット・サイズをセットし CMD レジスタをセットしてデータ送信を開始します。ユーザ回路は送信 FIFO へ送信データを全て転送し Busy フラグが'0' ネゲートするのを監視します。現在の送信コマンドが完了した後に、次の送信コマンドに向けユーザ回路は IPコアをリセットすることなく、TDL/PKL の値を更新できます。

- b) データ受信の場合、ユーザ回路は受信 FIFO ステータスを監視し受信 FIFO が空の状態でなければ受信データをリードします。

#### サーバー・モード(SRV[0]='1')

サーバー・モードにおいてはクライアント・モードとの違いは通信ターゲットの MAC アドレスを獲得する初期化プロセスにあります。クライアント・モードでは MAC アドレスは UDP10G-IPコアが送信した ARP 要求後に受信した ARP 応答から抽出します。一方サーバー・モードでは MAC アドレスはターゲット IP アドレスに合致した相手からの ARP 要求での送信元 MAC アドレスから抽出します。初期化後のデータ送信および受信についてはクライアント・モードと同一です。サーバー・モードでの動作シーケンス例を以下に示します。

- 1) RST レジスタを'1'にセットし本 IP コアをリセット状態とします。

- 2) SML/SMH レジスタで自身の MAC アドレス、DIP/SIP レジスタで相手/自分の IP アドレス、DPN/SPN レジスタでポート番号を設定します。

- 3) RST レジスタ='0'としてコアのリセット状態を解除します。UDP10G-IPコアは相手 MAC アドレスを獲得するため ARP 要求を待ちます、そして相手からの ARP 応答を返送します。この初期化が完了すると Busy フラグが'0'ネ ゲートされます。

- 4) データ送受信はクライアント・モードと同一です。

## コアの検証方法

本 IP コア製品には Intel 純正の評価ボードで実機動作する Quartus II リファレンス・デザイン・プロジェクトが同梱されているため、実ボードでの動作確認が可能です。 また、ドキュメントで示されていない細かい信号タイミング等については、リファレンス・デザインに Signal TAP を追加して実機動作させることで、実波形を観測・確認することが可能です。

## 必要とされる環境と設計スキルについて

本 IPコアの実機動作確認やデザイン・ゲートウェイ社へのサポート依頼には Intel 純正の対応評価ボードが必要となるため、ユーザ側でコア購入時に手配してください。 また、Intel 社の 10Gb MAC-IPコアも別途必要となりますのでご注意ください。

本コアを使ってユーザ・システムを設計・実装するためには、HDL 言語設計技術・UDP プロトコル知識および Quartus ツールによるデザイン実装経験を必要とします。

## 注文情報

本製品は Intel 代理店から、あるいはデザイン・ゲートウェイ社から直接購入することが可能です。 また、デバイス・ファミリに応じて現在以下のコアのラインナップが用意されています。 それ以外のファミリに対応した UDP10G-IP コアにつきましては DesignGateway 社までお問い合わせください。

#### 表 6: コアのラインナップ

| コア型番          | 対応ファミリ  | 対応評価ボード名        | 対応評価ボード型番         |

|---------------|---------|-----------------|-------------------|

| UDP10G-IP-A10 | Arria10 | Arria10GX 開発キット | DK-DEV-10AX155S-A |

## 改版履歴

| リビジョン | 日付          | 履歴                    |

|-------|-------------|-----------------------|

| 1.0   | Sep-19-2017 | New release           |

| 1.0J  | 2017/11/13  | Rev1.0 に対応した日本語翻訳版を発行 |