### USB3.0 IP デバイス側 プロトコル&リンクレイヤ・コア

2015/05/14 Product Specification Rev 1.2J

#### Design Gateway Co.,Ltd

本社: 〒184-0012

東京都小金井市中町 3-23-17

電話/FAX: 050-3588-7915 E-mail: sales@dgway.com URL: <u>www.dgway.com</u>

### 特長

- USB3.0 規格 Revision1.0 の SuperSpeed (5.0Gbps)

通信機能を実装

- デバイス用コントローラを提供

- リンク・レイヤおよびプロトコル・レイヤを包含

- フィジカル・レイヤは TI 社製 PHY チップ(TUSB1310A)と直接インタフェ ース

| Core Facts               |                                     |  |  |  |  |  |

|--------------------------|-------------------------------------|--|--|--|--|--|

|                          | コアの提供情報                             |  |  |  |  |  |

| 提供ドキュメント                 | リファレンスデザイン・マニュアル                    |  |  |  |  |  |

| 提供形態                     | 暗号化 HDL ファイル                        |  |  |  |  |  |

| サンプル                     | インスタンス化サンプル・プロジェクト                  |  |  |  |  |  |

| リファレンスデザイン               | Quartus II/NIOS II プロジェクト           |  |  |  |  |  |

| アプリケーション情報               | (リファレンスデザインマニュアルに記載                 |  |  |  |  |  |

| その他                      | ALTERA 評価ボードによる実機検証可                |  |  |  |  |  |

|                          | ArriaV GX スタータ開発キット用                |  |  |  |  |  |

|                          | Cyclone V E FPGA 開発キット用             |  |  |  |  |  |

|                          | Cyclone IV GX FPGA 開発キット用           |  |  |  |  |  |

|                          | Arria II GX FPGA 開発キット用             |  |  |  |  |  |

|                          | (Design Gateway 製 AB08-USB3HSMC カード |  |  |  |  |  |

| が必要                      |                                     |  |  |  |  |  |

| 技術サポート                   |                                     |  |  |  |  |  |

| デザインゲートウエイ・ジャパンによる国内サポート |                                     |  |  |  |  |  |

- コア周波数は PIPE 接続部は 250MHz、内部は 125MHz 以上で選択可能

- USB 3.0 PIPE インタフェース 16bit サポート

- 最大 15 個の IN/OUT エンドポイントをサポート

- コントロール 1 個

- o IN/OUT 各 7 個

- 全ての転送タップをサポート(Control 転送、Bulk 転送、Isochronous 転送、Interrupt 転送)

- シンプルな Host プロセッサ向けトランザクション I/F および DMA I/F

- ALTERA 評価ボードによる購入前のコア実機評価が可能

- 安心の国内サポート

### 表1: コンパイル結果(コントロール 1 個, IN/OUT 各 2 個)

| Family       | Example Device  | Fmax<br>(MHz) | Combinational ALUTs <sup>1</sup> / Logic Elements | Registers <sup>1</sup> | Pin² | Block Memori<br>bit | PLL | Design<br>Tools |

|--------------|-----------------|---------------|---------------------------------------------------|------------------------|------|---------------------|-----|-----------------|

| CycloneIV GX | EP4CGX150DF31C7 | 135           | 8,910                                             | 3,864                  | 68   | 135,168             | 2   | QuartusII 13.1  |

| Arria II GX  | EP2AGX125EF35C4 | 149           | 5,793                                             | 3,864                  | 68   | 135,168             | 2   | QuartusII 10.1  |

| CycloneV E   | 5CEFA7F31I7     | 140           | 5,907                                             | 4,389                  | 68   | 135,168             | 2   | QuartusII 14.0  |

| ArriaV GX    | 5AGXFB3H4F35C4  | 138           | 5,905                                             | 4,266                  | 68   | 135,168             | 2   | QuartusII 14.0  |

#### 備老·

- 1) 実際のロジック消費カウントはユーザロジックやフィット条件等に依存します

- 2)このサンプルはコアと TI\_PHY 接続用回路の全 I/O とクロックがチップ外部と直接インターフェイスし、その他、内部信号は FF で取り囲んだケースでのコンパイル結果となります

- 3)コアのエンドポート数は可変です. Bulk 転送 FIFO 量は各1個へ削減可能です.

<sup>\*</sup> LTSSM: Link Training and Status State Machine, LFPS: Low Frequency Periodic Signaling

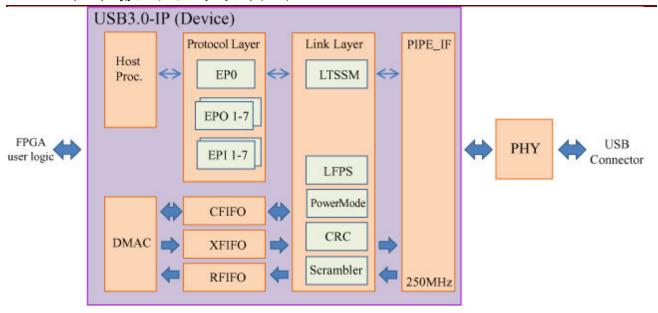

図1: USB3.0 IP ブロック図

### アプリケーション情報

本コアは、低コストで 5.0Gbps の広帯域を必要とする USB3.0 対応デバイス・システムに最適です。本 IP ではほとんどの USB3.0 プロトコル(規格書の第6章の一部と第7章,第8章)をハードウェアで処理するため、ローエンド CPU での処理が可能となり、また、構成パラメータにより、最小限のエンドポイントで実現可能なデバイス(マスストレージクラスなど)から多数のエンドポイントが必要なハイエンドなデバイスまで柔軟に対応可能です。 本コアは USB2.0(480Mbps)およびそれ以前の低速規格をあえて省略し FPGA 内での占有リソースを最小限に抑えているため、5.0Gbps の広帯域通信を最も低コストで実装するソリューションを提供します。

### 概略

USB3.0 IP デバイス側コアはリンク・レイヤとプロトコル・レイヤを内蔵し、Host プロセッサが用意したメモリ上のデータのアドレス,転送長などをコア内蔵のレジスタへセットするだけで、パケットへの分割、CRC&スクランブルの付加、USB バス上のフロー制御などをコアのハードウェアが処理し、処理結果をレジスタへ反映します。データの受信も同様に処理されます。

IP コアの Host インタフェースはシンプルなレジスタアクセス・インタフェースで構成され、メモリへのシンプルな DMA アクセス・インタフェースを具備し、簡単に NIOS II プロセッサや ALTMEMDDR への接続が行えます。

PHY チップとの接続は、標準的な PIPE インタフェースに準拠しており、FPGA ポートとのタイミング調整用の Flip-Flop を経由して、ほぼそのまま接続が可能です。

IP コア内部のクロックは転送処理速度の関係から 125MHz 以上(125M×4 バイト=500MB/S)、PHY チップとの接続は 250MHz 固定(500MHz×2バイト)となっていますが、Host インタフェースや DMA インタフェースは必要な同期化を行った後、低速クロックでの接続が可能です。

### USB3.0 IP デバイス側の内部ブロックの説明

USB3.0 IP デバイス側コアは大きく3つのブロックで構成されています。

### プロトコル・レイヤ(Protocol Layer)

プロトコル・レイヤは、Host プロセッサからレジスタで指定されたメモリ上のデータの管理と、それを USB3.0 のパケットへ分割し、リンク・レイヤへ送信します。 受信はその逆です。 必要なホスト(PC などホストバスアダプタ) との End-to-End のシーケンス番号やクレジット処理はこのレイヤで行われます。

#### • EP0(エンドポイントO)

USB3.0 で規定されたコントロール転送を処理します。 すなわち、セットアップ・パケットの受領、コントロール用のデータ転送(IN/OUT)、ステータス転送の処理を行います。

#### EPO(エンドポイント・アウト1~7)

BULK-OUT, INTERRUPT-OUT, ISOCHRONOUS-OUT の各転送を処理します。

### • EPI(エンドポイント・イン1~7)

BULK-IN, INTERRUPT- IN, ISOCHRONOUS-IN の各転送を処理します。

#### MPP(マルチ・パーパスポイント)

U0 状態への遷移直後の Port-Capabilities, Port-Configuration/Response の送受信処理の他、必要なアプリケーションでは Isochronous Time Stamp(ITS)や Link Management Packet(LMP)等の送受信処理にも使用します。

#### FIFO

CFIFO は EPO のデータ転送専用のデータ送受信 FIFO であり、XFIFO は EPI で共用されるデータ送信 FIFO(最大2面/自動アサイン)、RFIFO は EPO で共用されるデータ受信 IFO(最大2面/自動アサイン)です。

#### DMAC,各種アービタ

各エンドポイントからの DMA 要求、パケット送受信要求はプロトコル・レイヤ内部で調整され順次処理されます。

#### リンク・レイヤ(Link Layer)

リンク・レイヤは、プロトコル・レイヤからのパケットに各種 CRC(CRC-5/16/32)を付加し、スクランブルを掛け、8B(×4)シンボルで PIPE\_IF へ送信します。リンク間の送受信、フロー管理もここで処理されます。

#### LTSSM ブロック

USB3.0 で規定されたリンクの状態を管理し、初期化とパワー状態のシーケンス処理を行います。

#### FLOW ブロック

リンク間のフロー制御を行います。すなわち Link Command を使って、リンク間の転送の正常・異常、リトライおよびクレジット処理を行います。

### LFPS ブロック

初期化時やパワーモードからの復帰時の、LFPS(Low Frequeency Periodic Signaling)の送出処理、受領処理を行います。

#### • Power Mode ブロック

パワーモードへ投入時の、Link Command の送受信処理を行います。

#### • 送受信処理ブロック

パケット送受信時に、CRC の付加/確認、スクランブルの付加/解除、Link Control ワードの付加/確認などを行います。

#### パイプ・インターフェース(PIPE Interface)

パイプ・インターフェースは、リンク・レイヤとの各種データや信号を、PIPE クロックに同期して PHY へ送受信します。 受信はその逆です。

#### 送信ブロック

8B(×4)シンボルを8B(×2)シンボルへ変換しシンボルの Elastic 処理や SKIP オーダーセットの挿入もここで行います。(内部が125MHz 動作の場合、PHY のクロックとの微妙な周波数差から送信側でも Elastic 処理が必要です。)

#### • 受信ブロック

送信の逆の処理を行います。

#### • 制御ブロック

リンク・レイヤの状態遷移などに応じて必要な信号を PIPE クロックに同期させて送ります。また、PHY からの信号を内部クロックに再同期してリンク・レイヤへ送ります。

### FPGA 内部コントローラ(FPGA Controller)

FPGA 内部コントローラとしては一般的にはアプリケーション・ソフトウエアを実行する Host プロセッサが使われ、 USB3.0 IP デバイス側コアをレジスタアクセスすることで、 USB のデバイス・フレームワークより上位の制御(規格書の第9章以降)を構成を管理します。 システム・コントローラは Host プロセッサ、 DMA インタフェース、メモリなどから構成されます。

### **USB3.0 PHY**

PHY は USB3.0 対応の外付けチップ(TI 製 TUSB1310A)を使用します。

# IP コアの I/O 信号説明

コアの I/O 信号はユーザ回路と柔軟に接続できるようにするため、信号のみ定義され特定デバイスやピンには固定されておりません。 下表 2 にコアの全 I/O 信号を説明します。なお、特に断りのない信号は正論理です。

### 表2: IP コアの I/O 信号

| 信号名            | 方向 | 説明                                                         |

|----------------|----|------------------------------------------------------------|

|                |    | 共通インターフェイス信号                                               |

| RST_N          | In | コアのロジックをリセットするリセット信号、負論理。                                  |

| CLK            | In | IP コアの動作クロック。(125MHz)                                      |

| PCLK           | In | PIPE のクロック。(250MHz)                                        |

|                |    | PHY チップの生成する PIPE 用のクロックと同一の周波数(DCM 等で位相調整可)を入れる。また、PCLK 停 |

|                |    | 止中は定常的に動作するクロック(CLK など)に切り替えてよい。                           |

| I_EPO_ENB[7:1] | In | エンドポイント・アウト(EPO)の実装・未実装を定義する。                              |

|                |    | 最大7個実装でき、[1] EPO1, [7]EPO7 に対応する。1の時実装。                    |

| I_EPI_ENB[7:1] | In | エンドポイント・イン(EPI)の実装・未実装を定義する。                               |

|                |    | 最大7個実装でき、[1] EPI1, [7]EPI7 に対応する。1の時実装。                    |

(表 2: IP コアの I/O 信号 - 共通インターフェイス信号)

| 信号名               | 方向              | 説明                                                    |  |  |  |  |  |

|-------------------|-----------------|-------------------------------------------------------|--|--|--|--|--|

|                   | PIPE インターフェイス信号 |                                                       |  |  |  |  |  |

| O_PIPE_READY      | Out             | PIPE クロック(PCLK)の動作中を示す。                               |  |  |  |  |  |

|                   |                 | P3 以外のステートに遷移後、I_PHY_STATUS_ASYN の立ち上がりを検出してアサートする。   |  |  |  |  |  |

| O_RX_TERMINATION  | Out             | 受信終端の有無を制御する。1の時に終端有り。                                |  |  |  |  |  |

|                   |                 | PCLK に非同期に変化する。(PCLK 停止中でも変化する。)                      |  |  |  |  |  |

| O_TX_DETRX_ASYN   | Out             | 相手の受信終端の有無の検出を制御する。                                   |  |  |  |  |  |

|                   |                 | PCLK に非同期に変化し、P3 ステート時近辺(O_PIPE_READY ネゲート)で使用する。     |  |  |  |  |  |

| O_TX_EIDLE_ASYN   | Out             | 送信信号(SSTXP/SSTXN)を電気的アイドル状態へ制御する。                     |  |  |  |  |  |

|                   |                 | PCLK に非同期に変化し、P3 ステート時近辺(O_PIPE_READY ネゲート)で使用する。     |  |  |  |  |  |

| O_PWR_DOWN_ASYN[  | Out             | PHY のパワーステートを制御する。00:P0, 01:P2, 10:P3, 11:P3          |  |  |  |  |  |

| 1:0]              |                 | PCLK に非同期に変化し、P3 ステート時近辺(O_PIPE_READY ネゲート)で使用する。     |  |  |  |  |  |

| O_TX_DETRX_LPBK   | Out             | 相手の受信終端の有無の検出を制御する。                                   |  |  |  |  |  |

|                   |                 | PCLK に同期して変化し、P3 ステート時近辺以外(O_PIPE_READY アサート)で使用する。   |  |  |  |  |  |

| O_TX_ELECIDLE     | Out             | 送信信号(SSTXP/SSTXN)を電気的アイドル状態へ制御する。                     |  |  |  |  |  |

|                   |                 | PCLK に同期して変化し、P3 ステート時近辺以外(O_PIPE_READY アサート)で使用する。   |  |  |  |  |  |

| O_POWER_DOWN      | Out             | PHY のパワーステートを制御する。00:P0, 01:P2, 10:P3, 11:P3          |  |  |  |  |  |

| [1:0]             |                 | PCLK に同期して変化し、P3 ステート時近辺以外(O_PIPE_READY アサート)で使用する。   |  |  |  |  |  |

| I_PWRPRESENT      | In              | VBUS に電源が供給されている状態を入力する。PCLK に非同期に入力。                 |  |  |  |  |  |

| I_RX_ELECIDLE     | In              | 受信信号(SSRXP/SSRXN)の電気的アイドル状態を入力する。PCLK に非同期に入力。        |  |  |  |  |  |

| I_PHY_STATUS_ASYN | In              | PHY の各種状態の入力を制御する信号を入力する。PCLK に非同期に入力。                |  |  |  |  |  |

|                   |                 | P3 ステートからの遷移後、PCLK の動作開始を検出する為に使用する。                  |  |  |  |  |  |

| I_RX_STATUS011_AS | In              | 相手の受信終端の有無の検出結果を入力する。PCLK に非同期に入力。                    |  |  |  |  |  |

| YN                |                 | 1の時受信終端は有り。                                           |  |  |  |  |  |

| I_PHY_STATUS      | In              | PHY の各種状態の入力を制御する信号を入力する。PCLK に同期して入力。                |  |  |  |  |  |

|                   |                 | O_PIPE_READY のアサート中に、受信終端の有無の検出完了を表示する。               |  |  |  |  |  |

| I_RX_STATUS011    | In              | 相手の受信終端の有無の検出結果を入力する。PCLK に同期して入力。                    |  |  |  |  |  |

|                   |                 | I_PHY_STATUS が1の時に有効で、1の時受信終端は有り。                     |  |  |  |  |  |

| O_TX_DATAK[1:0]   | Out             | 送信シンボル(8B コード)が K コードか、D コードかを示す。1 の時 K コード。PCLK に同期。 |  |  |  |  |  |

| O_TX_DATA[15:0]   | Out             | 送信シンボル(8Bコード)の2シンボル分。PCLKに同期。                         |  |  |  |  |  |

| I_RX_VALID        | In              | 受信シンボルが有効なタイミングを示す。1の時有効。PCLK に同期。                    |  |  |  |  |  |

| I_RX_DATAK[1:0]   | In              | 受信シンボル(8B コード)が K コードか、D コードかを示す。1 の時 K コード。PCLK に同期。 |  |  |  |  |  |

| I_RX_DATA[15:0]   | In              | 受信シンボル(8B コード)の2シンボル分。PCLK に同期。                       |  |  |  |  |  |

(表 2: IP コアの I/O 信号 - PIPE インターフェイス信号)

| 信号名                 | 方向                  | 説明                                                           |  |  |  |  |  |

|---------------------|---------------------|--------------------------------------------------------------|--|--|--|--|--|

|                     | ホスト・レジスタ・インターフェイス信号 |                                                              |  |  |  |  |  |

| I_LINK_REG_RE[15:0] | In                  | リンクレイヤの制御レジスタのリード信号。                                         |  |  |  |  |  |

|                     |                     | 16 本分あるが全て実装されている訳ではない。1本は4バイト。 CLK に同期し1サイクルアサートする。         |  |  |  |  |  |

| I_LINK_REG_WE[15:0] | In                  | リンクレイヤの制御レジスタのライト信号。                                         |  |  |  |  |  |

|                     |                     | 16 本分あるが全て実装されている訳ではない。1本は4バイト。CLK に同期し1サイクルアサートする。          |  |  |  |  |  |

| I_PRTE_REG_RE[15:0] | In                  | プロトコルレイヤの制御レジスタのリード信号。                                       |  |  |  |  |  |

|                     |                     | 16 本分あるが全て実装されている訳ではない。1本は4バイト。 CLK に同期し1サイクルアサートする。         |  |  |  |  |  |

| I_PRTE_REG_WE[15:0] | In                  | プロトコルレイヤの制御レジスタのライト信号。                                       |  |  |  |  |  |

|                     |                     | 16 本分あるが全て実装されている訳ではない。1本は4バイト。 CLK に同期し1サイクルアサートする。         |  |  |  |  |  |

| I_XPP_REG_RE[511:0] | In                  | 各エンドポイントの制御レジスタのリード信号。                                       |  |  |  |  |  |

|                     |                     | 各 32 本分あるが全て実装されている訳ではない。1本は4バイト。 CLK に同期し1サイクルアサートする。       |  |  |  |  |  |

| I_XPP_REG_WE[511:0] | In                  | 各エンドポイントの制御レジスタのライト信号。                                       |  |  |  |  |  |

|                     |                     | 各 32 本分あるが全て実装されている訳ではない。1本は4バイト。 CLK に同期し1サイクルアサートする。       |  |  |  |  |  |

| O_EP_REG_RD[31:0]   | Out                 | 全制御レジスタのリードデータを示す。何れかの_RE がアサートした次サイクルで有効。                   |  |  |  |  |  |

| I_EP_REG_WD0[31:0]  | In                  | 制御レジスタへのライトデータを入力する。何れかの_WE がアサートしたタイミングで有効。                 |  |  |  |  |  |

| I_EP_REG_WD1[31:0]  | In                  | 制御レジスタへのライトデータを入力する。何れかの_WE がアサートしたタイミングで有効。                 |  |  |  |  |  |

|                     |                     | EPI4~7,EPO4~7 を使用する場合に I_EP_REG_WDO と論理的に同じ信号を接続する。 負荷分散の為、異 |  |  |  |  |  |

|                     |                     | なる FF と接続することが望ましい。                                          |  |  |  |  |  |

| O_EP_IRQ            | Out                 | USB コアからの割り込み信号。1の時割り込み、レベル信号。                               |  |  |  |  |  |

| O_EXT_CNTL [1:0]    | Out                 | USB コア外部制御用の信号。リンク・レイヤの制御レジスタで ON/OFF できる。                   |  |  |  |  |  |

| O_LANE_POL          | Out                 | RX Lane Porarity 制御信号 1: 反転, 0; 非反転                          |  |  |  |  |  |

| I_USB20_RESET       | In                  | USB2.0 からのリセットを入力。1でリセット。USB2.0 コアがない場合はOに固定する。              |  |  |  |  |  |

(表 2: IP コアの I/O 信号 - ホスト・レジスタ・インターフェイス信号)

| 信号名               | 方向                  | 説明                                                                     |  |  |  |  |  |

|-------------------|---------------------|------------------------------------------------------------------------|--|--|--|--|--|

|                   | DMA アクセス・インターフェイス信号 |                                                                        |  |  |  |  |  |

| I_DMAC_IDLE       | In                  | 次の DMA アクセス開始が可能な状態を示す。                                                |  |  |  |  |  |

| O_DMAC_REQ        | Out                 | DMA アクセスの開始を示す。CLK に同期し1サイクルアサートする。                                    |  |  |  |  |  |

| O_DMAC_ADR [31:0] | Out                 | DMA の開始アドレスを示す。O_DMAC_REQ アサート時に有効。                                    |  |  |  |  |  |

| O_DMAC_U2M        | Out                 | DMA の方向を示す。O_DMAC_REQ アサート時に有効。                                        |  |  |  |  |  |

|                   |                     | 0: Memory to USB, 1: USB to Memory。                                    |  |  |  |  |  |

| O_DMAC_LEN[8:0]   | Out                 | DMA の長さを示す。O_DMAC_REQ アサート時に有効。                                        |  |  |  |  |  |

|                   |                     | 0x100: 256 ワード(4K バイト)、0x001: 1ワード(4 バイト)                              |  |  |  |  |  |

| O_DMAC_BE [3:0]   | Out                 | 各バイトの有効/無効。                                                            |  |  |  |  |  |

| O_DMAC_DONE       | Out                 | データ転送の完了を示す。最終データ転送の完了数サイクル後に1サイクルアサートする。                              |  |  |  |  |  |

| I_DMAC_M2U_VLD    | In                  | DMA が Memory to USB の場合に、I_DMAC_M2U_DATA の有効なタイミングを示す。                 |  |  |  |  |  |

| I_DMAC_M2U_DATA[3 | In                  | DMA が Memory to USB の場合に、メモリからのデータを入力する。                               |  |  |  |  |  |

| 1:0] or [63:0]    |                     | モードはトップモジュールの verilogの PARAMETER "DMA64_MODE"で調整できる。                   |  |  |  |  |  |

|                   |                     | I_DMAC_M2U_VLD=1'b1 のタイミングで4バイト分(又は 8 バイト)の転送が完了する。(wait はない)          |  |  |  |  |  |

| I_DMAC_U2M_WAIT   | In                  | DMA が USB to Memory の場合に、メモリがデータを受け付けられないタイミングを示す。                     |  |  |  |  |  |

| O_DMAC_U2M_OUT    | Out                 | DMA が USB to Memory の場合に、O_DMAC_U2M_DATA の有効なタイミングを示す。                 |  |  |  |  |  |

| O_DMAC_U2M_DATA[  | Out                 | DMA が USB to Memory の場合に、メモリへのデータを出力する。                                |  |  |  |  |  |

| 31:0] or [63:0]   |                     | モードはトップモジュールの verilogの PARAMETER "DMA64_MODE"で調整できる。                   |  |  |  |  |  |

|                   |                     | O_DMAC_U2M_OUT=1'b1, I_DMAC_U2M_WAIT=1'b0 のタイミングで4バイト分(又は 8 バイト)の転送が完了 |  |  |  |  |  |

|                   |                     | する。                                                                    |  |  |  |  |  |

(表 2: IP コアの I/O 信号 - DMA アクセス・インターフェイス信号)

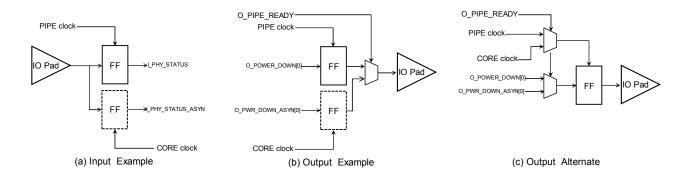

### PIPE インターフェイスの注意点

一般的な PIPE インタフェースですが、外付け PHY チップと接続する場合は信号の同期・非同期に注意が必要です。(図2参照)

入力信号には PHY からの PIPE クロック(PCLK)停止中でも参照する信号があり、その様な信号はピンと直接あるいは、コア内部のクロックで動作する FF で再同期した信号とします(\_ASYN 付)。 PIPE クロック動作中は PIPE クロックに同期して参照する信号がある場合は2系統に分ける必要があります。

出力信号にも PIPE クロック(PCLK)停止中でも変化する信号があり、その様な信号はピンと直接あるいは、コア内部のクロックで動作する FF で再同期して出力します。(ASYN 付)。 PIPE クロック動作中は同期して出力する信号がある場合は、ピンの直前で MUX するか、切り替えクロックで動作する FF で同期して出力します。

図2: PIPE インターフェース接続例

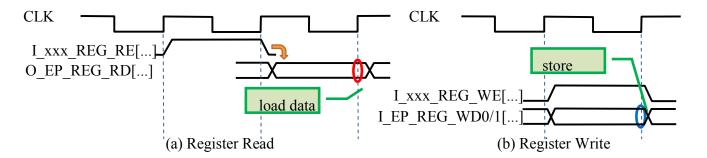

## ホスト・レジスタ・インターフェイスのタイミング

レジスタ・アクセスは図3されるように、アクセスしたいレジスタに相当する I\_xxx\_REG\_RE を1サイクルアサート するとそのレジスタのリード値が O\_EP\_REG\_RD に出力されます。また、I\_xxx\_REG\_WE を1サイクルアサートしながらレジスタへのライト値を I EP REG WD に入力すると書き込みが行われます。

図3: ホスト・レジスタ・インターフェイスの信号波形

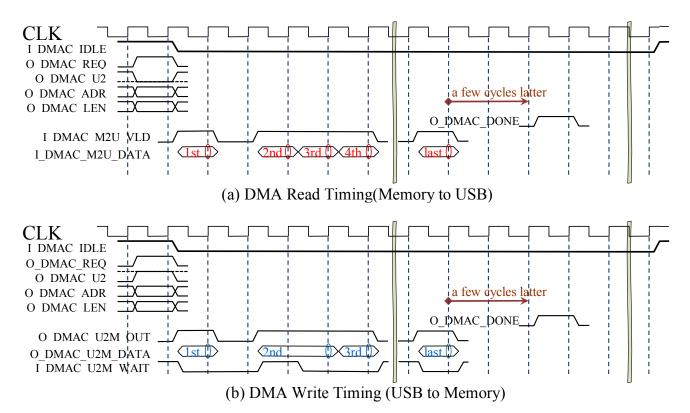

### DMA アクセス・インターフェイスのタイミング

DMA アクセスは図4示されるように、I\_DMAC\_IDLE がアサートの時、O\_DMAC\_REQ が1サイクルアサートされます。この時、同時にアクセスアドレス、方向および長さが指定されます。

転送方向に応じて適宜 VLD,WAIT 信号等を使用してフロー制御が行われながらデータを転送します。 指定された長さの転送が完了すると、しばらく(数サイクル)して、O\_DMAC\_DONE が1サイクルアサートされ、 DMA アクセスが完了します。

図4: DMA アクセス・インターフェイスの信号波形

# IP コアの制御レジスタ説明

下表4に Host プロセッサからアクセス可能なコアの制御レジスタを説明します。

### 表4: IP コアの制御レジスタ

| レジ     | スタ名         | R/W     | オフセット     | 説明                                                             |

|--------|-------------|---------|-----------|----------------------------------------------------------------|

| リンク    | ・レイヤし       | ノジスタ    | [ADDRESS= | C_BASEADDR+LINK_BASE+OFFSET]                                   |

| LINK_C | CNFG        | R/W     | 0h        | リンク・レイヤ構成レジスタ.                                                 |

|        | USE         | _VALID  | [0]       | USB バス(LTSSM)の状態の SS_Disable 以外への遷移を可能とする。(動作可能状態)             |

|        | PN          | /ID_ENB | [1]       | ホスト側からの Power Mode 遷移要求を受け付け可能とする。                             |

|        | SC          | RB_DIS  | [2]       | スクランブルを行わない。デバッグ用。                                             |

|        | E           | XT_CNT  | [5:4]     | O_EXT_CNTL [1:0](I/O 信号参照)を ON/OFF する。                         |

|        | U2_INA      | CT_CNT  | [15:8]    | U1 から U2 へ遷移する時間(U2_Inactive_timer)のカウントを指定する。                 |

|        |             |         |           | Value=実時間/(USB_CLK× 0x10000)                                   |

| LINK_C | ONTL        | W       | 1h        | リンク・レイヤ制御レジスタ. 1 ライトで指示する。未記載のビットは0とする。                        |

|        | GO_         | RXDET   | [0]       | USB バス(LTSSM)の状態を SS_Disable から Rx_Detect_Active へ遷移させる。(動作開始) |

|        |             |         |           | 事前に、LINK_CNFG[USB_VALID]を ON しておくこと.                           |

|        | GC          | _RCOV   | [3]       | Active_U0 状態から Recovery 状態へ遷移させる。                              |

|        | GO_PMI      | D_NUM   | [9:8]     | GO_PMD で遷移させるパワーモードレベルを指定する。01:U1, 10:U2, 11;U3                |

|        | G           | O_PMD   | [10]      | パワーモードへの遷移を要求する。成功/非成功はホスト側の状態などによる。                           |

|        |             | GO_U0   | [11]      | パワーモード(Active_U1/U2/U3)からの復帰を指示する。                             |

| LINK_I | RQE         | R/W     | 2h        | リンク・レイヤ割り込みレジスタ                                                |

|        |             | IRQ     | [0]       | 割り込み要求中。Read Only.                                             |

|        |             | ENB     | [1]       | IRQ が1の時、外部への割り込み信号(O_EP_IRQ。I/O 信号参照)を ON する。                 |

| LINK_L | TSSM        | R       | 3h        | リンク・レイヤ状態レジスタ                                                  |

|        |             | RCOV    | [6:0]     | リンク・レイヤがリカバリ(Recovery)状態へ遷移した要因を示す。ビット7が ON の間保持する。            |

|        | IRQ_FACTOR  |         | [15:7]    | リンク・レイヤが割り込んだ要因を表示。ただし、リンク・レイヤの状態は CPU の指示に関わらず変化する            |

|        |             |         |           | 可能性がある。 何れかのビットが ON の時、LINK_IRQE[IRQ]が ON となる。 該当ビットへの1ライトでクリ  |

|        |             |         |           | ア。                                                             |

|        | LTSSM       |         | [28:24]   | 現在のリンク・レイヤ状態を表示する。状態は USB3.0 仕様に準拠。コード割り当ては別途。                 |

|        | DEV_ADR_OFF |         | [30]      | USB のデバイスアドレスがO(未設定)である。なお、デバイスアドレスは一度設定しても、リンク・レイヤ状態          |

|        |             |         |           | が SS_Disable,Rx_Detect_Reset へ遷移した場合は、ハードウェアによってクリアされる。        |

|        |             | US_OFF  | [31]      | 現在の VBUS が OFF 状態である。                                          |

(表 4: IP コアの制御レジスタ - リンク・レイヤレジスタ)

| レジ                                                  | スタ名   | R/W    | オフセット   | 説明                                                    |  |  |

|-----------------------------------------------------|-------|--------|---------|-------------------------------------------------------|--|--|

| プロトコル・レイヤレジスタ [ADDRESS=C_BASEADDR+PRTE_BASE+OFFSET] |       |        |         |                                                       |  |  |

| PRTE.                                               | CNFG  | R/W    | 0h      | プロトコル・レイヤ構成レジスタ.                                      |  |  |

|                                                     | DE    | EV_ADR | [6:0]   | USB バスのデバイスアドレスを設定する。なお、デバイスアドレスは一度設定しても、リンク・レイヤ状態が   |  |  |

|                                                     |       |        |         | SS_Disable,Rx_Detect_Reset へ遷移した場合は、ハードウェアによってクリアされる。 |  |  |

| PRTE                                                | CNTL  | W      | 1h      | プロトコル・レイヤ制御レジスタ. 1 ライトで指示する。未記載のビットは0とする。             |  |  |

|                                                     | ARBT  | RESET  | [0]     | プロトコル・レイヤのアービタのリセットを指示する。デバッグ用。                       |  |  |

| PRTE                                                | _IRQE | R/W    | 2h      | プロトコル・レイヤ割り込み許可レジスタ                                   |  |  |

|                                                     |       | EP0    | [0]     | EP からの割り込みを許可する。                                      |  |  |

|                                                     |       | EPO    | [7:1]   | EPO1~7 からの割り込みを許可する。[1]: EPO1, [7]:EPO7               |  |  |

|                                                     |       | MPP    | [16]    | MPP からの割り込みを許可する。                                     |  |  |

|                                                     |       | EPI    | [23:17] | EPI1~7 からの割り込みを許可する。[17]: EPI1, [23]:EPI7             |  |  |

| PRTE.                                               | _IRQ  | R      | 3h      | プロトコル・レイヤ割り込み許可レジスタ                                   |  |  |

|                                                     |       | EP0    | [0]     | EPO から割り込みを要求中。 IRQE の該当ビットが1の時、外部への割り込み信号を ON する。    |  |  |

|                                                     |       | EPO    | [7:1]   | EPO1~7 からの割り込みを要求中。IRQE の該当ビットが1の時、外部への割り込み信号を ON する。 |  |  |

|                                                     |       |        |         | [1]: EPO1, [7]:EPO7                                   |  |  |

|                                                     |       | MPP    | [16]    | MPP からの割り込みを要求中。IRQE の該当ビットが1の時、外部への割り込み信号を ON する。    |  |  |

|                                                     |       | EPI    | [23:17] | EPI1~7 からの割り込みを要求中。IRQE の該当ビットが1の時、外部への割り込み信号を ON する。 |  |  |

|                                                     |       |        |         | [17]: EPI1, [23]:EPI7                                 |  |  |

| DMA_E                                               | BASE  | R/W    | 4h      | DMA ベースレジスタ                                           |  |  |

|                                                     |       | BASE   | [31:28] | DMA を行うメモリアドレスの上位ビット                                  |  |  |

(表 4: IP コアの制御レジスタ - プロトコル・レイヤレジスタ)

| レジ     | スタ名              | R/W    | オフセット  | 説明                                                                      |

|--------|------------------|--------|--------|-------------------------------------------------------------------------|

|        |                  |        |        | [ADDRESS=C_BASEADDR+XP_BASE+(0x80 × 0)+0x000+OFFSET]                    |

|        | EPO_CNFG R/W 00h |        |        | EPO 構成レジスタ.                                                             |

| 2. 0_0 | VALID            |        | [0]    | EPを動作可能状態とする。可能状態でない時でも、Setup DP パケットを受信した場合は Setup Data は正             |

|        |                  |        |        | しく受信し、"SETUP_IP"状態へ遷移し、INVALID が ON となる。                                |

|        |                  |        |        | そのまま"SETU_IP"状態をクリアすると、WRDY パケットが返信される。                                 |

|        | AUTO_9           | SETUP  | [1]    | SETUP 状態からソフトウェアの介入なしに SETUP acknowledge を送信し遷移する. 0: OFF, 1 : ON       |

|        | AUTO_F           | RESUL  | [2]    | RESEULT 状態からソフトウェアの介入なしに IDLE 状態へ遷移する. 0:OFF, 1 :ON                     |

|        | _                | Т      |        |                                                                         |

|        | AUTO_            | STALL  | [3]    | STALLED 状態からソフトウェアの介入なしに STALL acknowledge を送信し遷移する. 0: OFF, 1: ON      |

|        |                  | ED     |        |                                                                         |

| EP0_C  | NTL              | R/W    | 01h    | EP0 制御レジスタ。状態の表示と全ビットの更新が行える。                                           |

|        |                  |        |        | [13:0]の何れかのビットが ON で割り込み要求中。[23:16]は検出状態。[31:24]は過渡状態。                  |

| EP0_C  | LR               | W      | 02h    | EPO 制御レジスタクリア。1ライトで該当ビットをクリアする。                                         |

| EP0_S  | ET               | W      | 03h    | EP0 制御レジスタセット。1ライトで該当ビットをセットする。                                         |

|        | R                | RESULT | [0]    | RESULT 状態。通常クリアすると最後の ACK パケットが返信される。その後 IDLE へ戻る。                      |

|        |                  |        |        | STALL が ON の場合は、STALL パケット、VALID が OFF の場合は、NRDY パケットが返信される。            |

|        |                  | SETUP  | [1]    | SETUP_IP 状態。Setup DP パケットを受信した状態、SETUP0/1 レジスタに8バイトの内容が格納されてい           |

|        |                  |        |        | る。 クリアすると ACK パケット(NumP=1)が返信される                                        |

|        |                  |        |        | ただし、RETRY が ON の場合(Setup DP パケット受信エラー)は retry 付き、INVALID が ON の場合(VALID |

|        |                  |        |        | 参照)は NumP=0 で返信される。その後、INRDY/OUTRDY 等の指示に従い、所定の状態へ遷移する。                 |

|        | ST               | ALLED  | [8]    | STALLED 状態。クリアすると STALL パケットが返信される。                                     |

|        | DEF              | ERRED  | [9]    | DEFERRED 状態。Deferred ビット付きのパケットを受信するとこの状態へ遷移する。クリアすると ERDY              |

|        |                  |        |        | パケットが返信されて、所定の状態へ遷移する。                                                  |

|        |                  | WRDY   | [10]   | WRDY 状態。NRDY パケットなどを送信した後(flow 状態)この状態になる。クリアすると ERDY パケットが返            |

|        |                  |        |        | 信されて、所定の状態へ遷移する。                                                        |

|        | WAIT             | Γ_RECV | [14]   | 何らかのパケット待ち状態。BUSY が ON の時有効                                             |

|        |                  | BUSY   | [15]   | (IDLE 状態もしくは[13:0]状態)以外の時 ON。WAIT_RECV が ON の時、本ビットをクリアすると IDLE 状態へ     |

|        |                  |        | 57     | 戻る。また、どんな状態でも[14]と本ビットを一緒にクリアすると IDLE 状態へ戻る。                            |

|        |                  | STALL  | [16]   | STALL パケットを受信するか、何らかの異常を検出した。                                           |

|        |                  | OVER   | [17]   | ホストの転送量がEPO_DLEN での指定より多い。(デバイス側が少ない)                                   |

|        |                  | UNDER  | [18]   | ホストの転送量がEPO_DLEN での指定より少ない。(デバイス側が多い)                                   |

|        | SEND_            |        | [19]   | AUTO_STALLED が ON の場合に、STALLED 状態で STALL を送信した.,                        |

|        |                  | RETRY  | [24]   | 受信した DP パケット(SetupDP パケット含む)にエラーがあった。                                   |

|        | II .             | NVALID | [25]   | VALID が OFF の時に、Setup DP パケットを受信した。                                     |

|        |                  | NRDY   | [27]   | RESULT 状態から NRDY を送信した。                                                 |

| EP0_D  | LEN              | R/W    | 04h    | EPO データ長設定レジスタ                                                          |

|        |                  | DLEN   | [20:0] | 設定したデータ長。                                                               |

|        |                  | EOB    | [29]   | IN 転送時に、最終パケットに EOB(End Of Burst)ビットを付ける。                               |

|        | 0                | UTRDY  | [30]   | OUT 転送(ホストからデバイス)指示。                                                    |

| EDA -  | LEN              | INRDY  | [31]   | IN 転送(デバイスからホスト)指示。                                                     |

| EP0_P  | LEN              | R      | 05h    | EPO データ長結果レジスタ                                                          |

|        |                  | PLEN   | [20:0] | 実際に転送したデータ長。                                                            |

|        | 0                | UTRDY  | [30]   | OUT 転送(ホストからデバイス)指示。(DLEN レジスタのコピー)                                     |

|        | FED              | INRDY  | [31]   | IN 転送(デバイスからホスト)指示。(DLEN レジスタのコピー)                                      |

| EP0_B  | -                | R/W    | 06h    | EPO データ長バッファ(メモリアドレス)レジスタ                                               |

|        |                  | BADDR  | [27:8] | データを入出力するメモリの先頭アドレス                                                     |

### USB3.0 IP デバイス側 プロトコル&リンクレイヤ・コア

| EP0_9 | SEQN   | R/W    | 07h    | EPO シーケンス番号レジスタ                 |

|-------|--------|--------|--------|---------------------------------|

|       |        | SEQN   | [4:0]  | パケットの現在のシーケンス番号。ライトもできるが通常必要ない。 |

| EP0_5 | SETUS0 | R/W    | 09h    | EP0 セットアップデータレジスタ0              |

| EP0_5 | SETUS1 | R/W    | 0Ah    | EPO セットアップデータレジスタ1              |

|       | SET    | TUP0/1 | [31:0] | SetupDP パケットで受信した内容。            |

(表 4: IP コアの制御レジスタ - エンドポイントゼロ・レジスタ)

| レジ                 | スタ名          | R/W     | オフセット                                                | 説明                                                                  |

|--------------------|--------------|---------|------------------------------------------------------|---------------------------------------------------------------------|

| エンドポイントアウト(EPO)レジス |              | PO)レジスタ | [ADDRESS=C_BASEADDR+XP_BASE+(0x80 × N)+0x000+OFFSET] |                                                                     |

| EPO_C              | EPO_CNFG R/W |         | 00h                                                  | EPO 構成レジスタ.                                                         |

|                    |              | VALID   | [0]                                                  | EP を動作可能状態とする。可能状態でない時に、DP パケットを受信した場合は NRDY パケットを送信した              |

|                    |              |         |                                                      | 後、WRDY 状態となる。                                                       |

|                    | I            | SOCHR   | [1]                                                  | Isochronous モードの転送を行う。                                              |

|                    |              | AGGR    | [2]                                                  | 受信 DP パケットのデータをメインメモリへ格納完了する前に、ACK パケットを返信するモード。                    |

|                    | AUTO_        | STALL   | [3]                                                  | STALLED 状態からソフトウェアの介入なしに STALL acknowledge を送信し遷移する. 0: OFF, 1 : ON |

|                    |              | ED      |                                                      |                                                                     |

|                    |              | BURST   | [18:16]                                              | バースト長の設定。4~1を設定する。                                                  |

|                    | FIF          | O_REQ   | [30]                                                 | EPO の受信用 FIFO のアービトレーション要求状態。デバッグ用。リードのみ。                           |

|                    | FIF          | O_LOC   | [31]                                                 | EPO が受信用 FIFO を専有するモード。デバッグ用。                                       |

| EPO_C              | NTL          | R/W     | 01h                                                  | EPO 制御レジスタ。状態の表示と全ビットの更新が行える。                                       |

|                    |              |         |                                                      | [13:0]の何れかのビットが ON で割り込み要求中。[23:16]は検出状態。[31:24]は過渡状態。              |

| EPO_C              | LR           | W       | 02h                                                  | EPO 制御レジスタクリア。1ライトで該当ビットをクリアする。                                     |

| EPO_S              | ET           | W       | 03h                                                  | EPO 制御レジスタセット。1ライトで該当ビットをセットする。                                     |

|                    |              | COMP    | [0]                                                  | COMP 状態(転送完了)。通常クリアすると IDLE へ戻る。 OUTRDY はクリアされる。 余分な DP パケットを受      |

|                    |              |         |                                                      | 信した場合は NRDY へ遷移する。                                                  |

|                    | ST           | ALLED   | [8]                                                  | STALLED 状態。クリアすると STALL パケットが返信される。                                 |

|                    | DEF          | ERRED   | [9]                                                  | DEFERRED 状態。 Deferred ビット付きのパケットを受信するとこの状態へ遷移する。 クリアすると ERDY        |

|                    |              |         |                                                      | パケットが返信されて、所定の状態へ遷移する。                                              |

|                    |              | WRDY    | [10]                                                 | WRDY 状態。NRDY パケットなどを送信した後(flow 状態)この状態になる。クリアすると ERDY パケットが返        |

|                    |              |         |                                                      | 信されて、所定の状態へ遷移する。                                                    |

|                    |              | NRDY    | [11]                                                 | NRDY 状態。NRDY パケット送信中。暫くすると WRDY 状態へ遷移する。                            |

|                    | WAI          | Γ_RECV  | [14]                                                 | 何らかのパケット待ち状態。BUSY が ON の時有効                                         |

|                    |              | BUSY    | [15]                                                 | (IDLE 状態もしくは[13:0]状態)以外の時 ON。WAIT_RECV が ON の時、本ビットをクリアすると IDLE 状態へ |

|                    |              |         |                                                      | 戻る。また、どんな状態でも[14]と本ビットを一緒にクリアすると IDLE 状態へ戻る。                        |

|                    |              | STALL   | [16]                                                 | STALL パケットを受信するか、何らかの異常を検出した。                                       |

|                    |              | OVER    | [17]                                                 | ホストの転送量が DLEN より多い。(デバイス側が少ない)                                      |

|                    |              | UNDER   | [18]                                                 | ホストの転送量が DLEN より少ない。(デバイス側が多い)                                      |

|                    |              | RETRY   | [24]                                                 | 受信した DP パケット(SetupDP パケット含む)にエラーがあった。                               |

|                    | I            | NVALID  | [25]                                                 | IDLE 状態の時 DP パケットが受信できない状態でを受信した。(VALID or OTRDY が OFF)             |

| EPO_D              | PO_DLEN R/W  |         | 04h                                                  | EPO データ長設定レジスタ                                                      |

|                    |              | DLEN    | [20:0]                                               | 設定したデータ長。                                                           |

|                    |              | UTRDY   | [30]                                                 | OUT 転送(ホストからデバイス)指示。COMP 状態(経由して NRDY,ERDY 状態)でクリアされる。              |

| EPO_P              | PLEN         | R       | 05h                                                  | EPO データ長結果レジスタ                                                      |

|                    |              | PLEN    | [20:0]                                               | 実際に転送したデータ長。0以外の時は何か受信した事を示す。                                       |

|                    |              | UTRDY   | [31]                                                 | OUT 転送(ホストからデバイス)指示。(DLEN レジスタのコピー)                                 |

| EPO_B              | FFR          | R/W     | 06h                                                  | EPO データ長バッファ(メモリアドレス)レジスタ                                           |

|                    |              | BADDR   | [27:8]                                               | データを入出力するメモリの先頭アドレス                                                 |

| EPO_S              | EPO_SEQN R/W |         | 07h                                                  | EPO シーケンス番号レジスタ                                                     |

| COMP_SEQN | [4:0]   | 転送完了(ACK 送信済み)したパケットのシーケンス番号。ライトもできるが通常必要ない。 |

|-----------|---------|----------------------------------------------|

| BFR_SEQN  | [12:8]  | バッファ(メモリ)へ格納したパケットのシーケンス番号。ライトもできるが通常必要ない。   |

| RCV_SEQN  | [20:16] | 受信したパケットのシーケンス番号。ライトもできるが通常必要ない。             |

# (表 4: IP コアの制御レジスタ - エンドポイントアウト・レジスタ)

| レジ                                                                    | スタ名     | R/W    | オフセット                  | 説明                                                                  |

|-----------------------------------------------------------------------|---------|--------|------------------------|---------------------------------------------------------------------|

| エンドポイントイン(EPI)レジスタ [ADDRESS=C_BASEADDR+XP_BASE+(0x80×N)+0x400+OFFSET] |         |        |                        |                                                                     |

| EPI_CNFG R/W 00h                                                      |         | 00h    | EPI 構成レジスタ.            |                                                                     |

|                                                                       |         | VALID  | [0]                    | EP を動作可能状態とする。可能状態でない時に、ACK パケットを受信した場合は NRDY パケットを送信し              |

|                                                                       |         |        |                        | た後、WRDY 状態となる。                                                      |

| ISOCHR                                                                |         | [1]    | Isochronous モードの転送を行う。 |                                                                     |

|                                                                       | RE      | START  | [2]                    | ホストが設定転送長に達する前に、ACK(NumP=0)パケットを送ってきた場合に、EPIを自動的に再起動し               |

|                                                                       |         |        |                        | て残りの受信待ちになるモード。 OFF の場合は UNDER が ON となり COMP 状態へ遷移する。               |

|                                                                       | AUTO_   | STALL  | [3]                    | STALLED 状態からソフトウェアの介入なしに STALL acknowledge を送信し遷移する. 0: OFF, 1 : ON |

|                                                                       |         | ED     |                        |                                                                     |

|                                                                       |         | BURST  | [18:16]                | バースト長の設定。4~1を設定する。                                                  |

|                                                                       | FI      | O_REQ  | [30]                   | EPI の送信用 FIFO のアービトレーション要求状態。デバッグ用。リードのみ。                           |

|                                                                       | FIF     | O_LOC  | [31]                   | EPI が送信用 FIFO を専有するモード。デバッグ用。                                       |

| EPI_CN                                                                | NTL     | R/W    | 01h                    | EPI 制御レジスタ。状態の表示と全ビットの更新が行える。                                       |

|                                                                       |         |        |                        | [13:0]の何れかのビットが ON で割り込み要求中。[23:16]は検出状態。[31:24]は過渡状態。              |

| EPI_CL                                                                | _R      | W      | 02h                    | EPI 制御レジスタクリア。1ライトで該当ビットをクリアする。                                     |

| EPI_SE                                                                | T       | W      | 03h                    | EPI 制御レジスタセット。1ライトで該当ビットをセットする。                                     |

|                                                                       |         | COMP   | [0]                    | COMP 状態(転送完了)。通常クリアすると IDLE へ戻る。INRDY はクリアされる。余分な ACK パケットを受        |

|                                                                       |         |        |                        | 信した場合は NRDY へ、EOB 付 DP パケットを送信した場合は WRDY へ遷移する。                     |

|                                                                       | STALLED |        | [8]                    | STALLED 状態。クリアすると STALL パケットが返信される。                                 |

|                                                                       | DEF     | ERRED  | [9]                    | DEFERRED 状態。 Deferred ビット付きのパケットを受信するとこの状態へ遷移する。 クリアすると ERDY        |

|                                                                       |         |        |                        | パケットが返信されて、所定の状態へ遷移する。                                              |

|                                                                       |         | WRDY   | [10]                   | WRDY 状態。 NRDY パケットなどを送信した後(flow 状態)この状態になる。 クリアすると ERDY パケットが返      |

|                                                                       |         |        |                        | 信されて、所定の状態へ遷移する。                                                    |

|                                                                       |         | NRDY   | [11]                   | NRDY 状態。NRDY パケット送信中。暫くすると WRDY 状態へ遷移する。                            |

|                                                                       | WAI     | Γ_RECV | [14]                   | 何らかのパケット待ち状態。BUSY が ON の時有効                                         |

|                                                                       |         | BUSY   | [15]                   | (IDLE 状態もしくは[13:0]状態)以外の時 ON。WAIT_RECV が ON の時、本ビットをクリアするとIDLE 状態へ  |

|                                                                       |         |        | 57                     | 戻る。また、どんな状態でも[14]と本ビットを一緒にクリアすると IDLE 状態へ戻る。                        |

|                                                                       |         | STALL  | [16]                   | STALL パケットを受信するか、何らかの異常を検出した。                                       |

|                                                                       |         | OVER   | [17]                   | ホストの転送量が DLEN より多い。(デバイス側が少ない)                                      |

|                                                                       |         | UNDER  | [18]                   | ホストの転送量が DLEN より少ない。(デバイス側が多い)                                      |

|                                                                       |         | RETRY  | [24]                   | Retry 付の ACK パケットを受信した。                                             |

|                                                                       |         | NVALID | [25]                   | IDLE 状態の時 DP パケットが送信できない状態で ACK パケットを受信した。(VALID or INRDY が OFF)    |

|                                                                       |         | ART_IP | [26]                   | RESTART 処理中。                                                        |

| EPI_DL                                                                | -EN     | R/W    | 04h                    | EPIデータ長設定レジスタ                                                       |

|                                                                       |         | DLEN   | [20:0]                 | 設定したデータ長。                                                           |

|                                                                       |         | EOB    | [29]                   | IN 転送時に、最終パケットに EOB(End Of Burst)ビットを付ける。                           |

|                                                                       |         | INRDY  | [31]                   | IN 転送(デバイスからホスト)指示。COMP 状態(経由して NRDY,ERDY 状態)でクリアされる。               |

| EPI_PL                                                                | EN .    | R      | 05h                    | EPIデータ長結果レジスタ                                                       |

|                                                                       |         | PLEN   | [20:0]                 | 実際に転送したデータ長。O以外の時は何か送信した事を示す。                                       |

|                                                                       |         | INRDY  | [31]                   | IN 転送(デバイスからホスト)指示。(DLEN レジスタのコピー)                                  |

| EPI_BF                                                                |         | R/W    | 06h                    | EPI データ長バッファ(メモリアドレス)レジスタ                                           |

|                                                                       |         | BADDR  | [27:8]                 | データを入出力するメモリの先頭アドレス                                                 |

### USB3.0 IP デバイス側 プロトコル&リンクレイヤ・コア

| EPI_S    | EQN   | R/W     | 07h                              | EPI シーケンス番号レジスタ                              |

|----------|-------|---------|----------------------------------|----------------------------------------------|

|          | COMP_ | SEQN    | [4:0]                            | 転送完了(ACK 受領済み)したパケットのシーケンス番号。ライトもできるが通常必要ない。 |

|          | BFR_  | SEQN    | [12:8]                           | バッファ(メモリ)から取り込んだパケットのシーケンス番号。ライトもできるが通常必要ない。 |

| TRN_SEQN |       | [20:16] | 送信したパケットのシーケンス番号。ライトもできるが通常必要ない。 |                                              |

|          | NUM_  | SEQN    | [28:24]                          | ACK でクレジットを与えられたパケットのシーケンス番号。ライトもできるが通常必要ない。 |

### (表 4: IP コアの制御レジスタ - エンドポイントイン・レジスタ)

| レジ       | スタ名                                                                     | R/W    | オフセット  | 説明                                                           |  |

|----------|-------------------------------------------------------------------------|--------|--------|--------------------------------------------------------------|--|

| マルチ      | マルチパーパスポイント(MPP)レジスタ [ADDRESS=C_BASEADDR+XP_BASE+(0x80×0)+0x400+OFFSET] |        |        |                                                              |  |

| MPP_C    | NFG                                                                     | R/W    | 00h    | MPP 構成レジスタ.                                                  |  |

|          |                                                                         | TRNS   | [0]    | MPP からパケットを送信する。完了するとクリアされる。Active_U0 になった時は、自動的に ON/OFF して、 |  |

|          |                                                                         |        |        | Port Capabilities, Port Configuration Response を送信。          |  |

| MPP_T    | HD0                                                                     | R/W    | 04h    | MPP 送信パケットO                                                  |  |

| MPP_T    | HD1                                                                     | R/W    | 05h    | MPP 送信パケット1                                                  |  |

|          | ٦                                                                       | ΓHD0/1 | [31:0] | 送信パケットのデータ。                                                  |  |

| MPP_RHD0 |                                                                         | R/W    | 06h    | MPP 受信パケットO                                                  |  |

| MPP_R    | HD1                                                                     | R/W    | 07h    | MPP 受信パケット1                                                  |  |

|          | F                                                                       | RHD0/1 | [31:0] | 受信パケットのデータ。                                                  |  |

| MPP_R    | CVD                                                                     | R/W    | 08h    | EPIシーケンス番号レジスタ                                               |  |

|          | MISC_RCNT [3:0]                                                         |        | [3:0]  | パケット受信で+1する。0xF になると0x0 へ戻る。ライトも可能。                          |  |

|          | MISC_RCVD_H                                                             |        | [7]    | 何かパケットを受信した。ONで割り込み要求。ライト可能。                                 |  |

|          | PCFG_RCVD                                                               |        | [30]   | Active_UO になって以降、Port Configuration を受信した。                   |  |

|          | PCAP_RCVD                                                               |        | [31]   | Active_U0 になって以降、Port Capabilities を受信。                      |  |

(表 4: IP コアの制御レジスタ - マルチパーパスポイント・レジスタ)

# IP コアの制御レジスタマップ

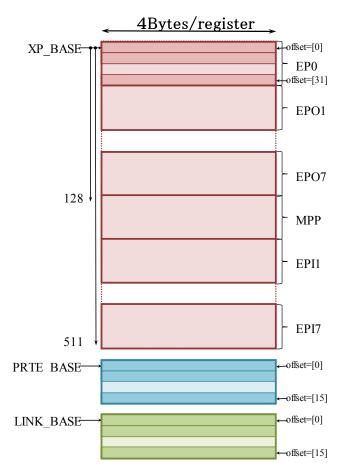

I\_xxx\_REG\_RE/WE[..]をアドレス順接続した場合のコアのレジスタ配置の概略を図5に示します。

図 5: IP コア内部レジスタのアドレス・マップ

#### IPコアの制御手順の概略

本コアを制御する主な手順について概略のみ説明します。

#### USB バス初期化

USB バスに接続された状態でデバイスが起動される、もしくは、起動後に USB バスに接続されると、バス動作を開始できます。その後、U0 ステートまでの概略手順を以下に示します。

- ① LINK\_LTSSM[VBUS\_OFF]で、VBUS の ON を確認する。

- ② LINK\_CNFG[USB\_VALID]で、動作可能状態とする。

- ③ LINK\_CNTL[GO\_RXDET]で、Rx\_Detect\_Active 状態への遷移を指示する。

- ④ ホスト側も動作可能であれば、自動的にリンクする。LINK\_LTSSM[LTSSM]で、Active\_U0 状態になればリンク成功。SS\_disable に戻れば②からリトライする

### USB デバイスのコンフィグレーション(Configured)状態まで

リンク成功後、EPO によるコントロール転送によって、コンフィグレーション(Configured)状態になるまでの概略手順を以下に示します。

- ① EPO\_CNFG[VALID]で、EPO を動作可能状態とする。

- □ SetupDP パケットが受信され、SETUP 状態となる。

- □ 最初の SetupDP は、SET\_ADDRESS でデータ転送なし。

- □ STATUS パケットを受信し、RESULT 状態となり、最終 ACK パケットを送信する。

- ② PRTE\_CNFG[DEV\_ADR]にデバイスアドレスをセットする。ハードウェアとしてはアドレス(Address)状態。

- ③ その後も、SetupDP パケット等のコントロール転送を何回か行う。

- □ コントロール転送がデータ転送を伴う場合は、送信データをメモリに設定するか(IN 転送)、受信バッファをメモリに確保して(OUT 転送)、EP0\_BFFR と EP0\_DLEN へ指示する。

- □ IN/OUT 転送の完了後、STATUS パケットを受信する。後はデータ転送なしと同様。

- ④ 最後に、SET\_CONFIGURATION を受領して、コンフィグレーション(Configured)状態となる。

#### USB デバイスの BULK\_IN, BULK\_OUT 転送

デバイスがコンフィグレーション(Configured)状態になった後、BULK\_IN(EPI)、BULK\_OUT(EPO)を使った転送です。転送内容自体はデバイス・クラス毎に異なります。以下は BULK\_OUT の場合で、BULK\_IN もほぼ同様です。

- EPO\_CNFG で、VALID を ON, バースト長を設定する。

- ② 受信バッファをメモリに確保して、EPO\_BFFR と EPO\_DLEN へ指示する。 DLEN には想定されるデータ長か、それ以上を設定する。

- ③ 何か受信すると、PLEN に受信データ長が表示されるので、受信バッファ内を確認する。 COMP 状態をクリアして、②へ戻る。

### コアの検証方法

USB3.0 IP デバイス側コアは DesignGateway 製 AB08-USB3HSMC ドータ基板と ALTERA 評価ボードの組み合わせによって実機での動作検証が可能です。(ただし HSMC の I/F 電圧を 2.5V に設定できる評価ボードのみ対応が可能となります。)

### 推奨される設計スキルに関して

本 IP をユーザ回路上に迅速・確実に実装するために、ALTERA の SOPC Builder および NIOS2EDS について の技術スキルを推奨します。また、高速インタフェース規格に関する一般的な知識を推奨します。更に、ハード ウェアデバッグには USB 3.0 規格のプロトコル仕様、ソフトウェア開発とデバッグには USB 規格のデバイス仕様 に関する知識・理解が必要です。

### 注文情報

| 品名                              | コア/製品型番       | 実機検証ボード/備考            |

|---------------------------------|---------------|-----------------------|

| USB3.0 デバイス側 IP コア Stratix-IV 版 | USB3D-IP-S4   | DK-DEV-4SGX230N       |

| USB3.0 デバイス側 IP コア Arria-II 版   | USB3D-IP-A2   | DK-DEV-2AGX125N       |

| USB3.0 デバイス側 IP コア Arria-V 版    | USB3D-IP-A5   | DK-START-5AGXB3N      |

| USB3.0 デバイス側 IP コア Cyclone-IV 版 | USB3D-IP-C4   | DK-DEV-4CGX150N       |

| USB3.0 デバイス側 IP コア Cyclone-V 版  | USB3D-IP-C5   | DK-DEV-5CEA7N         |

| HSMC 対応 USB3.0-IP デモ基板          | AB08-USB3HSMC | Altera 標準 HSMC アダプタ基板 |

本 USB3.0 IP デバイス側コアの価格やライセンス条件等の注文情報については国内 ALTERA 各代理店までお問い合わせください。

### 履歴

| リビジョン | 日付         | 更新内容                          |

|-------|------------|-------------------------------|

| 1.0   | 2011/09/09 | 日本語版の初版作成                     |

| 1.1J  | 2015/04/22 | コア内部レジスタを追加                   |

| 1.2J  | 2015/05/14 | ArriaV GX および Cyclone V E を追加 |

Copyright: 2012 Design Gateway Co,Ltd.