# ConfigROM とSDLink 混在の基板デザイン・ガイド

Ver1.0J 2017/09/28

本ドキュメントは SDLink を使った FPGA コンフィグレーション・システムにおいて、SDLink と FPGA 向け ConfigROM を混在するケースでの設計案について説明したものです。 例えば試作段階では SDLink を用いて開発し最終製品の段階で一般的な ConfigROM に切り替えてコンフィグレーションを 実行する場合などで適用できます。 切り替えにバス・スイッチを適用することで信号方向やコンフィグレーション電圧に依存せず柔軟性の高い混在コンフィグレーション環境を構築することができます。

## [目次]

| バス・スイッチについて                            | 1 |

|----------------------------------------|---|

| 基本的な接続方法                               | 2 |

| コンフィグレーション・クロック信号の注意点                  | 3 |

| nCONFIG/nPROG 信号の処理                    | 4 |

| CONF DONE/DONE および nSTATUS/nINIT 信号の処理 |   |

|                                        |   |

コンフィグレーションの SDLink と ConfigurationROM(以下 ROM とします)の切り替えにおいて、SDLink によるコンフィグレーションは FPGA がコンフィグレーション・クロック(CCLK/DCLK)を受信しますが ROM によるコンフィグレーションでは逆に FPGA がクロックを出力します。このように信号方向が切り替えによって変更される場合に最も使いやすいデバイスがバス・スイッチです。 本ドキュメントではコンフィグレーションの切り替えにバス・スイッチを応用した切り替え例を説明します。 汎用バス・スイッチとして Texas Instruments 社製 TS3A5018を使用した例にて説明します。

#### バス・スイッチについて

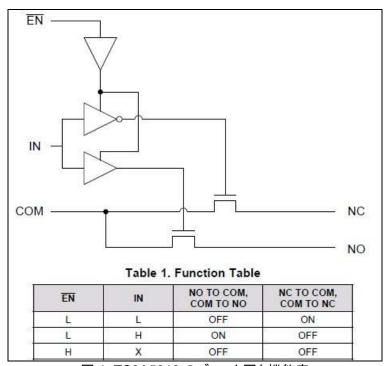

- 本例で紹介する TS3A5018 について説明します。

- このバス・スイッチは 2 対 1 の SPDT 機能を持つスイッチで、選択ピン(IN ピン)の H/L レベルで共通信号(COM ポート)に対して2つの接続先(NC ポートおよび NO ポート)を択一的に選択し接続します。

- 電源電圧は 1.8V~3.6V の範囲で使用できます。

- 接続した信号ポート間は低インピーダンス(10Ω程度)でショート接続します。

- 選択されない側のポートはハイ・インピーダンスとなり他ポートとは絶縁された状態となります。

- このため、信号の方向に関係なく接続と切断を電気的に選択できます。

- TS3A5018 は 4 チャネル分の 2 対 1SPDT スイッチ機能があります。

- 各ポートの信号レベル(コンフィグレーション電圧レベル)は 1.8V, 2.5V, 3.3V から選択できます。

- 下図 1 に TS3A5018 のブロック図(各チャネル)と機能を示します

図 1: TS3A5018 のブロック図と機能表

参考 URL: TS3A5018 紹介ページ: http://www.tij.co.jp/product/jp/TS3A5018

S

### 基本的な接続方法

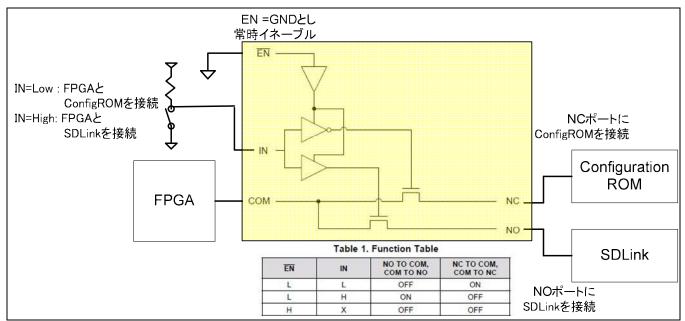

- 各コンフィグレーション信号について基本的な接続方法を図2に示します。

- TS3A5018 の選択ピン(IN)にて ROM を選択する(IN=Low)か SDLink を選択するか(IN=High)を選びます。

- 共通ポートの COM ポートに FPGA のコンフィグレーション信号を接続します。

- IN=Low 時に選択される NC ポート側に ROM のコンフィグレーション信号を接続します。

- IN=High 時に選択される NO ポート側に SDLink のコンフィグレーション信号を接続します。

- イネーブル(EN)は Low とし、常時 ROM または SDLink のいずれかが選択されます。

図 2: 基本的な接続方法

## コンフィグレーション・クロック信号の注意点

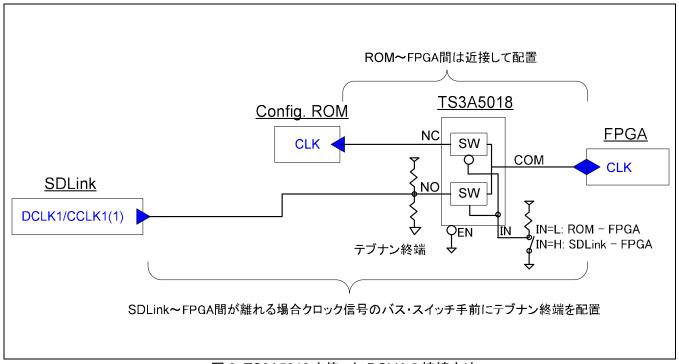

- コンフィグレーション・クロック(CCLK/DCLK)の信号方向は SDLink と ROM の場合で異なります。

- ROM は基本的に FPGA の近傍に配置しクロック信号が短くなるよう配慮します。

- 特にバス・スイッチと FPGA 間のクロック信号の配線長は極力短くします。

- SDLink は FPGA から離れた場所に配置せざるを得ない場合があります。

- この場合 SDLink からのコンフィグレーション・クロック信号の品質が悪化する恐れがあります。

- SDLink からのコンフィグレーション・クロックの配線長が長くなってしまう場合、バス・スイッチの NO ポート直近に テブナン終端を配置してください。

- この場合テブナン終端から FPGA までのクロック配線がスタブになりますがその距離を最小限に留めることで信号品質を維持します。

- クロック信号の接続イメージ例を下図3に示します。

図 3: TS3A5018 を使った DCLK の接続方法

#### nCONFIG/nPROG 信号の処理

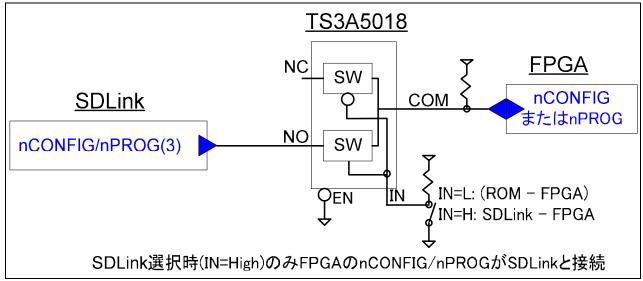

- コンフィグレーション開始信号(nCONFIG/nPROG)は ROM にはなく FPGA の接続先は SDLink のみですが、直結できません。

- その理由として ROM が選択されている場合であっても SDLink がこの開始信号をアサートしてしまうためです。

- 従って開始信号は SDLink が選択されている場合のみ FPGA と接続するようなデザインが必要です。

- バス・スイッチを使ったコンフィグレーション開始信号の接続例を下図4に示します。

- SDLink 選択時のみ開始信号を FPGA と接続する形であれば図 4 以外の方法であってもかまいません。

図 4: TS3A5018 を使った nCONFIG/nPROG 信号の接続方法

### CONF DONE/DONE および nSTATUS/nINIT 信号の処理

- コンフィグレーション完了信号(CONF\_DONE/DONE)およびコンフィグレーション・エラー信号(nSTATUS/nINIT) は ROM にはなく FPGA の接続先は SDLink のみです。

- この 2 種類の信号はどちらも FPGA から SDLink へ出力される信号であり、SDLink からは信号をドライブしないので FPGA と SDLink 間で直結できます。

- 従ってバス・スイッチ等の切り替え回路を挿入する必要はありません。

### ROM のみのコンフィグレーション信号の処理

● FPGA のコンフィグレーションの信号ピンにて、接続先が SDLink にはなく ROM のみの場合、バス・スイッチ等の 挿入なしで FPGA と ROM 間を直結できます。

# 改版履歴

| 版    | 日付         | 内容    |

|------|------------|-------|

| 1.0J | 2017/09/28 | 初期版発行 |

© 2017 Design Gateway Co,Ltd.