# クロック・ライン実装上のご注意

### <u>Ver1.0</u>

本アプリケーション・ノートにおいて、超高速/小型プログラマブル発振器[VariClock]を使ってクロックを発生する場合の、ユーザ基板側におけるクロック・ライン実装上の注意事項に関して説明します。

# [目次]

| 1: | VariClock の出力特性 | . 2 |

|----|-----------------|-----|

|    | クロック・ラインの終端     |     |

|    | クロック・ラインの配線パターン |     |

|    | クロックの負荷         |     |

|    | 結論              |     |

| •  |                 |     |

#### 1: VariClock の出力特性

VariClock は LVTTL レベルでクロックを出力します。 下表 1 に主な出力特性を示します。

| 項目      | 仕様               | 備考        |

|---------|------------------|-----------|

| 出力レベル   | High レベル 2.4V 以上 | LVTTL 出力  |

|         | Low レベル 0.4V 以下  |           |

| 出力電流    | ± 24mA           |           |

| 動作保証周波数 | 25MHz ~ 250MHz   | 出力負荷 20pF |

[表 1] VariClock の主な出力特性

VariClock の発振保証周波数の上限は 250MHz ですが、ユーザ基板と組み合わせての実用上のクロック上限周波数はユーザ基板のクロック・ラインの実装により大幅に変わります。 VariClock が駆動するクロック・ラインに十分な配慮がなされたユーザ基板においては、VariClock の能力を最大限引き出すことが可能です。 逆に適切でないクロック・ラインに VariClock が使われた場合、回路全体として使えるクロック周波数は VariClock の実力を大幅に下回ってしまいます。VariClock の能力を十分に発揮するためには、ユーザ基板においては以下の配慮が必要です。

- [1] クロック・ラインに適切な終端がなされているか

- [2] クロックの配線パターンは最適化されているか

- [3] クロックの負荷は適切な範囲内に抑えられているか

以下、それぞれの項目別に注意事項を説明します。 本アプリケーション・ノートは VariClock をクロック供給源として使う場合を前提としていますが、VariClock に限らず全てのクロック・システムに共通します。

#### 2: クロック・ラインの終端

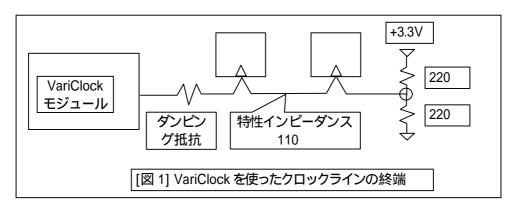

高速ボードにおいては、クロック・ラインの特性インピーダンスにマッチする終端が必要となります。 たとえばクロック・ラインの特性インピーダンスが 110 の場合においては、合成抵抗 110 のテブナン終端が効果的です。 その場合下図 1 のように実装してください。

終端抵抗の値は、VariClock モジュールの出力電流値が定格の $\pm$  24mA を超えないように選択してください。 図 1 の例では特性インピーダンス 110 のクロック・ラインに対して Pull-Up/Down 両側とも 220 のテブナン終端を実装しています。 この場合ダンピング抵抗を 0 とした場合でも、VariClock が High あるいは Low にドライブしたときの駆動電流は、3.3[V] / 220[ohm] = 15mA であり許容範囲の 24mA 以下となります。

一般的にクロック・ラインのパターン幅は広くし、特性インピーダンスを低く抑える必要があります。 それはラインの直流抵抗分を抑えることで振幅の減衰を最小限に留めるためと、外部からのノイズ耐性を向上するためです。 しかし特性インピーダンスは、上記 VariClock の駆動電流上限を超えないよう調整する必要があります。 たとえば特性インピーダンスを 50 としてしまうと、テブナン終端抵抗は 100 が必要となり 33mA の駆動電流が必要となりますが、これでは VariClock の能力を超えてしまいます。

VariClock の電流駆動能力との兼ね合いから、クロックの特性インピーダンスを 75 程度に調整し、テブナン終端抵抗を 150 とするのが最適です。 この場合の駆動電流は 22mA となり、許容範囲内です。

一方ダンピング抵抗の値は 22~39 程度が好ましいとされております。ダンピング抵抗の値を上げると波形のオーバーシュートは減りますがクロックの立ち上がり時間が遅くなり、またクロックの振幅が減少します。逆も同様のトレード・オフ関係があるので、回路にとって最適なクロック波形となるよう、ダンピング抵抗を調整することが推奨されます。

#### 3: クロック・ラインの配線パターン

最適なクロック・ラインを実装するために、ユーザ基板では以下の配慮が必要です。

- クロック・ラインはできるだけ短く配線する。

- 配線パターンは一筆書きパターンとし、配線途中にスタブを設けない。

- 経由ビア数は最小限に抑える。

- クロック・ラインの周囲に低インピーダンス信号である GND のガードパターンを設ける。

- クロック・ラインの配線層と隣り合う層は、できるだけ GND/VCC の低インピーダンス信号によるベタパターンの層とする。

- クロストーク・ノイズの影響を防ぐため、他の信号パターンはクロック・ラインの配線と並走しないよう実装する。

更に、同一クロックにおいて基板上に複数のクロック・チャネルが存在する場合、以下の配慮も必要となります。 ただし VariClock によるクロック出力は 1 チャネルしかないため、ユーザ基板上にクロックドライバを用意する必要があります。

- 全チャネルで特性インピーダンスと終端抵抗が等しくなるよう設計する。

- 全チャネルで配線距離が等長となるよう設計する。

- 全チャネルで負荷が同じになるよう接続デバイス数を調整する。

- 全チャネルで経由するビア数が等しくなるよう設計する。

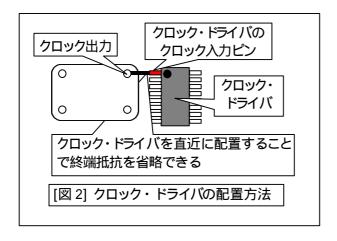

ユーザ基板上にクロックドライバを用意する場合、クロックドライバのクロック入力ピンは VariClock のクロック出力ピン(Pin#8)の直近となるよう、クロックドライバを下図 2 のように配置してください。そのように配慮することにより、VariClock のクロック出力(すなわちクロックドライバのクロック入力)信号における配線パターン長は最短となるため、この信号への終端抵抗を省略することが可能です。

#### 4: クロックの負荷

VariClock の動作保証周波数の上限は 250MHz ですが、それは負荷 20pF の場合です。 ユーザ基板上のクロック・ラインに接続される負荷により、実用上限の動作周波数はそれより低下します。 従ってクロックを供給するデバイス数が多い場合、クロックドライバを用いて各クロック・チャネルでの負荷を軽減する必要があります。

- 一般的なプリント基板においては、おおよその目安として以下を負荷として見積もることができます。

- [1] 配線 1cm につき 1pF

- [2] ビア1個につき1pF( )

クロック・ラインへは極力ビアを挿入しないよう設計してください。ビア部においては特性インピーダンスが変化するため、連続した均一の配線インピーダンスが維持できなくなり信号の反射が発生するためです。

すなわち、接続するデバイスのクロック入力ピンによる負荷の合計以外に、上記の負荷が加算されること になります。

許容される負荷はクロックの動作周波数に依存します。 たとえば VariClock 保証動作上限の 250MHz の クロックを使う場合、総負荷は 20pF 以下に抑える必要があります。 ユーザ基板のデバイスのクロック入 力ピンを仮に 15pF と仮定すると、接続可能なデバイス数は 1 デバイスのみとなります。 また、VariClock の出力ピン(Pin#8)自体で 1 個のスルホールを経由することになるので、それを 1pF の負荷とするとクロック配線長は約 4cm 以内とする必要があります。 ただもちろん、クロック配線長は短ければ短いほど良いの は言うまでもありません。

## 5: 結論

ユーザ基板のクロック・ラインを適切に設計することにより、VariClock の高いクロック発生能力を最大限に引き出すことが可能となります。