Super Low Latency Networking IPfor fintech

LL10GEMAC IP┃LLUDP10G IP┃LLTOE10G IP┃Document Download

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

specific requirements. Contact Us

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

specific requirements. Contact Us

DG's Low latency IP demo together with AMD's open-source reference design, Accelerated Algorithmic Trading (AAT) is now available on Alveo U50 and U250 Card. click for demo

For more detail, please Contact Us

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

specific requirements. Contact Us

Design Gateway’s Low Latency Networking IP is designed from the ground

up for very low latency requirements. Especially, FinTech applications

such as high-frequency trading (HFT), high speed trading (HST), Market

Data Processing and Tick-to-Trade (T2T) systems. We can provide total solutions

for low latency Networking IP cores and FPGA logic customization for application

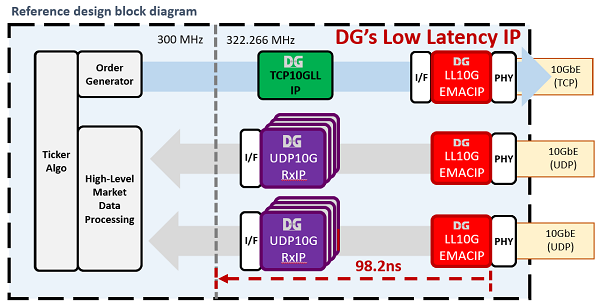

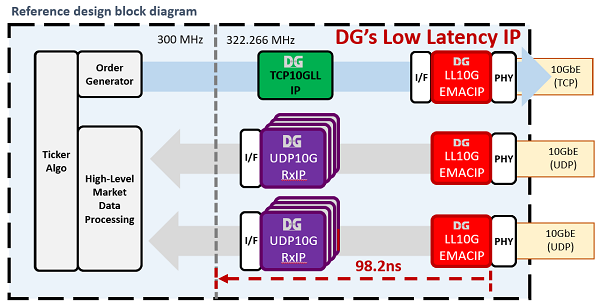

specific requirements. Contact UsAccelerated High Frequency Trading (HFT) reference design

DG's Low latency IP demo together with AMD's open-source reference design, Accelerated Algorithmic Trading (AAT) is now available on Alveo U50 and U250 Card. click for demo

Breaking Latency Barriers in Stock Trading with AMD AAT and DG Low-Latency IP cores Blog Article |

The Enhanced AMD's Stock Trading (AAT) demo by integrating DG's Low-Latency IP cores Blog Article |

Features

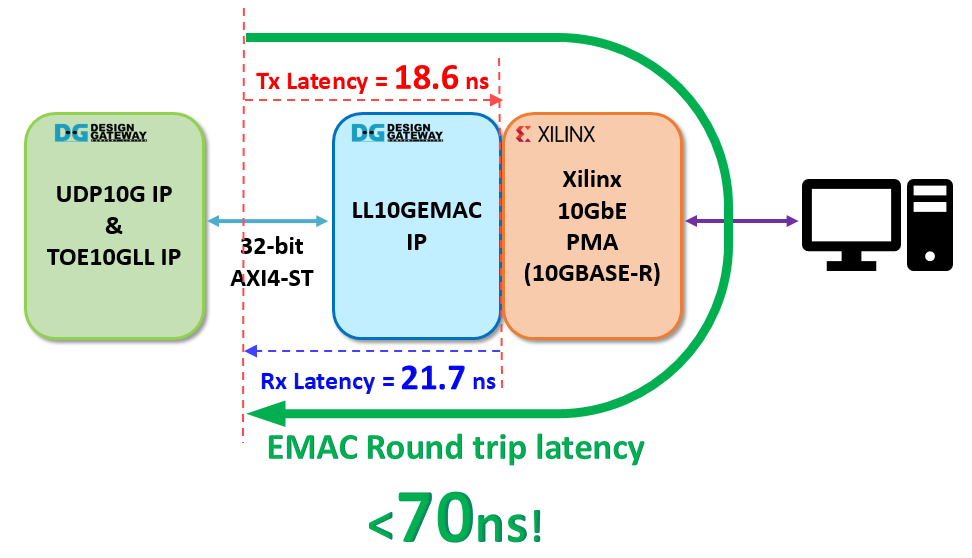

Low Latency 10GEMAC-IP (LL10GEMAC-IP)

|

DG LL 10G EMAC-IP with AMD’s AAT demo |

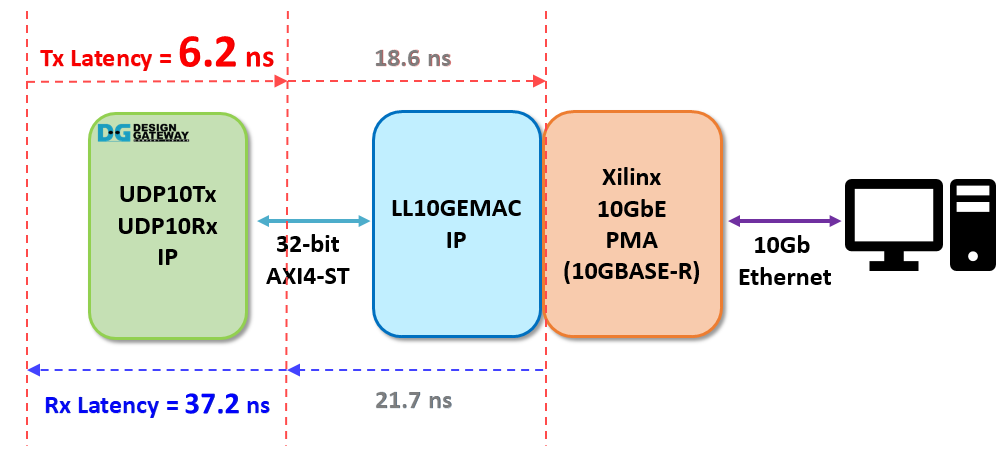

Low Latency UDP10G Rx/Tx-IP

|

DG LL UDP10GRx-IP 16 Sessions demo for FinTech |

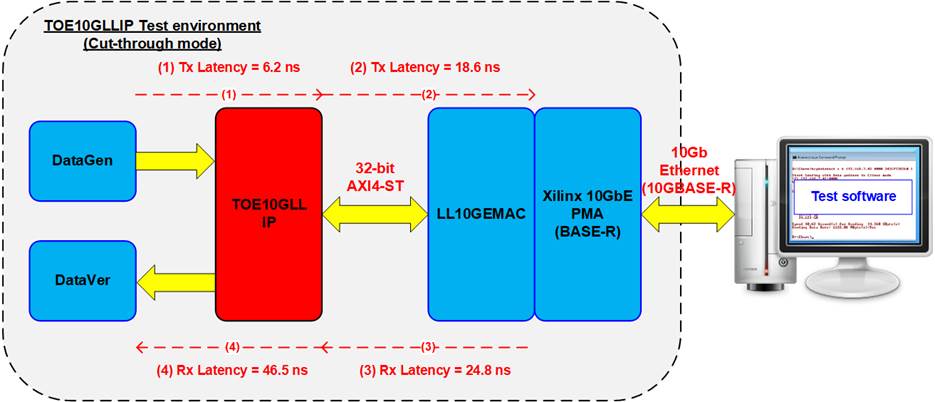

Low Latency TOE10G-IP (TOE10GLL-IP)

|

DG TOE10GLL-IP 32 Sessions demo |

Document download

| Document name | Update (Revision) |

| Presentation | 1.0E |

| Brochure | 2.6EX |

| IP core & Option | Datasheet | Reference Design Document | Demo Instruction Document | FPGA Board Setup | Free Evaluation demo file Contact Us | |

| Accelerated Algorithmic Trading (AAT) Demo |

Rev2.0 | Rev1.1 | U50 U250 |

|

||

|

|

||||||

| LL 10GEMAC-IP | Rev1.2 | Rev1.1 | Rev1.1 | Rev1.0 | ZCU102 | |

| Accelerated Algorithmic Trading (AAT) Demo |

Rev1.1 | Rev1.2 | U50 U250 |

|

||

|

|

||||||

| LL UDP10GRx-IP | Rev2.0 | Rev1.2 | Rev1.2 | Rev1.1 | ZCU102 KCU116 |

|

| 16 Session Demo | Rev1.0 | Rev1.0 | ZCU102 KCU116 |

|

||

|

|

||||||

| TOE10GLL-IP | Rev2.0 | Rev1.2 | Rev1.1 | ZCU102 ZCU106 |

||

| 32 Session Demo | Rev1.0 | Rev1.0 | ZCU102 ZCU106 |

|

||

For more detail, please Contact Us