USB3.0-IP core

Features┃Block diagram┃Document Download┃Applications

Please receive technical document update from DG News Letter. Subscribe to DG News

Please receive technical document update from DG News Letter. Subscribe to DG News

Technical document update page

Technical document update page

USB3.0(device)-IP

USB3.0(device)-IP

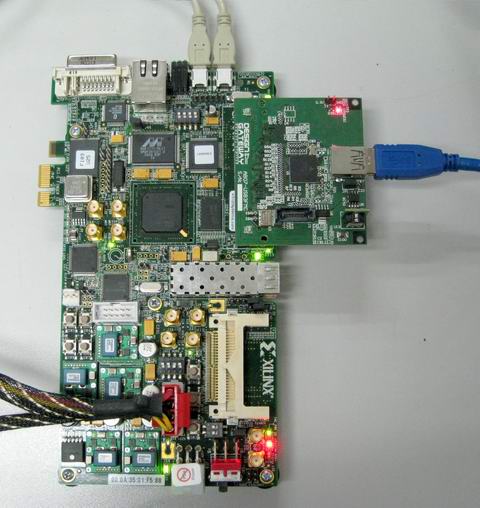

evaluation on SP605

Video Clip on Youtube

DesignGateway provide 1-hour limited Free bit file. You can evaluate USB3.0-IP

core on AMD FPGA boards before purchasing the IP core.

For the evaluation with AMD FPGA Boards, USB3.0-FMC adaptor board is necessary.(P/N: AB07-USB3FMC or AB07-USB3FMC-1.8VIF). Please ask Design Gateway.

Go to Registration page to get password

Go to Registration page to get password

USB3.0-IP core compliants with the USB 3.0 specification Revision1.0 and work on AMD

7-Series, Spartan-6 and Virtex-6 device.

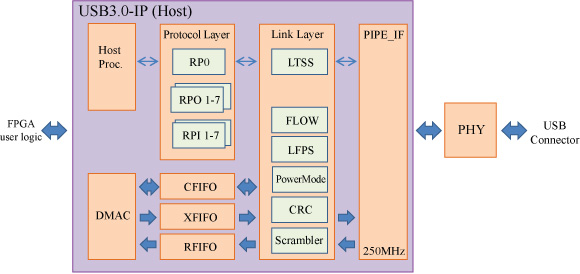

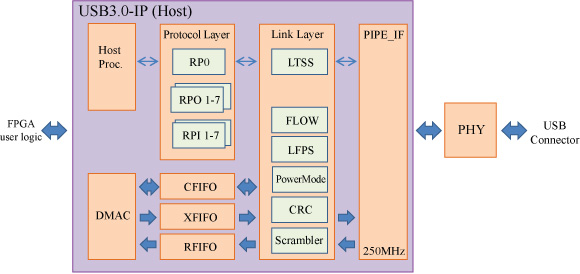

This IPcore provide link layer and protocol layer. Physical layer interfaces

to PHY chip by TI.

DesignGateway provide 1-hour limited bit file for AMD evaluation boards.

You can evaluate on AMD FPGA boards before purchasing the IPcore.

Features

- Compliant with the USB3.0 specification Revision1.0

- USB3.0 Host or Device Controller

- Implement link layer and protocol layer

- Physical layer interfaces to PHY chip by TI

** TI announce TUSB1310A is "NOT RECOMMENDED FOR NEW DESIGNS". Please see TI page - IP core clocks are adjustable (250MHz for PIPE I/F, more than 125MHz for internal)

- Support 16bit PIPE interface

- Support IN/OUT end point up to 15 points

- 1 point for control

- 7 points each for IN/OUT - Support All transmission taps (Control, Bulk, Isochronous and Interrupt transmission)

- Simple transaction interface with Host processor or DMA interface

- Able to evaluate on AMD FPGA boards before purchasing the IP core

Go to Registration page to get password

Go to Registration page to get password

Block diagram (Host side)

Document download

Common Documents

| Document name | Download |

| USB3.0-IP core Leaflet | Rev2.2 |

| USB3.0-IP core Presentation | Rev1.7 |

| FAT32 Data Recorder Presentation | Rev1.0 |

| AB07-USB3FMC Board Manual | Rev2.0 |

Technical Documents

| Support Devices | Zynq-7000 ZC706, Virtex-7 VC707, Kintex-7 KC705 Spartan-6 SP605, Virtex-6 ML605 |

||||

| IP core & Option |

Datasheet | Reference Design Document | Demo Instruction Document | Free Evaluation demo file * Ask password |

|

| USB3.0 Host-IP |

Rev1.4 | Rev1.0 | Rev1.4 | ZC706 VC707 KC705 SP605 ML605 |

|

| USB3.0 Device-IP |

Rev1.4 | Rev1.1 | Rev1.3 | ZC706 KC705 SP605 ML605 |

|

Free Bit file for evaluation

USB3.0(device)-IP

USB3.0(device)-IPevaluation on SP605

Video Clip on Youtube

For the evaluation with AMD FPGA Boards, USB3.0-FMC adaptor board is necessary.(P/N: AB07-USB3FMC or AB07-USB3FMC-1.8VIF). Please ask Design Gateway.

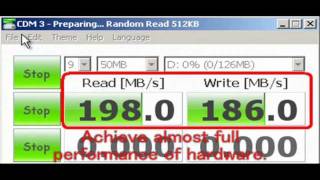

Performance

USB3.0-IP core can achieve maximum performance of current USB3.0 system.

USB3.0-IP core evaluation on SP605 USB3.0-IP core evaluation on SP605(with AB07-USB3FMC adaptor board) |

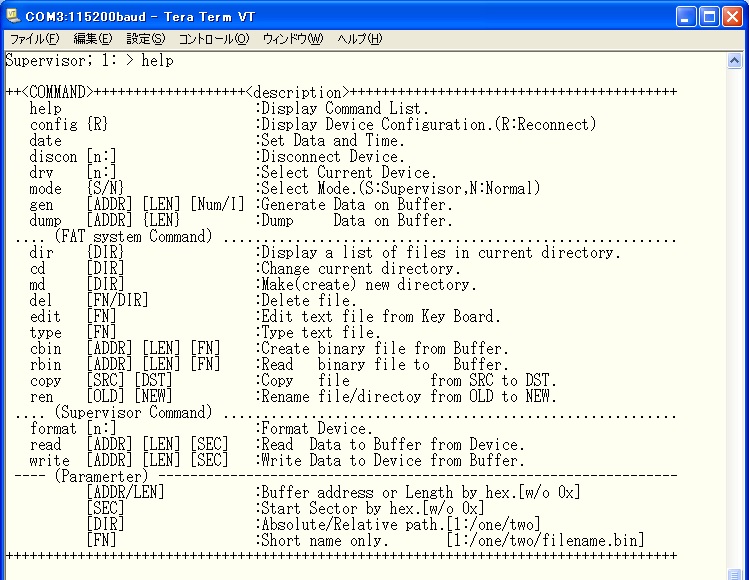

USB3.0-IP core Host Reference Design USB3.0-IP core Host Reference DesignSupport FAT32 commands |

Application: FAT32 data recording system (Device Side)

You can easily build FAT32 data recorder system with USB3.0 Device IP core.System Overview

Features

- PC recognizes as FAT32 external storage without any driver for Windows or Linux!

- FAT32 data recorder reference design is available.

- Free evaluation bit file for AMD FPGA boards.

Accessories

| Accessories for evaluation | Description |

| USB3.0-FMC adaptor board for AMD FPGA Boards USB3.0 TypeAtoA cable(1m) is attached. * Support FMC I/O voltage 2.5V only (does not support 1.8V-I/O such as VC707) |

|

| USB3.0-FMC adaptor board for AMD FPGA Boards USB3.0 TypeAtoA cable(1m) is attached. * Support FMC I/O voltage 1.8V only (for VC707) |