# Xilinx版10GEMAC-IPコアのご紹介 ver1.0J

2019/7/2 Design Gateway Page 1

### DG-10GEMAC-IPコア概要

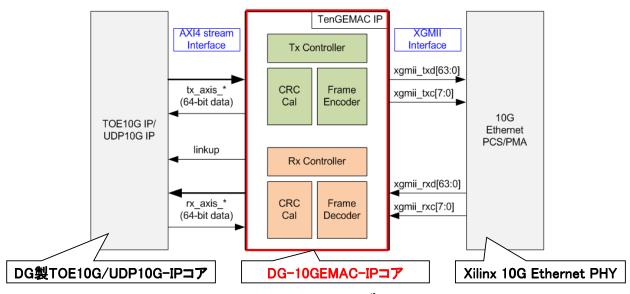

DG製IPコアと10G PHY間に挿入する10GEMACコア

DG-10GEMAC-IPコア・ブロック図

2019/7/2

Design Gateway

### DG-10GEMAC-IPコアの特長

- TOE10G-IPコア/UDP10G-IPコア専用MAC IPコア

- Xilinx製標準MAC(EF-DI-25GEMAC)と高い互換性

- 超低レイテンシ、送信19.2nsec、受信44.8nsec

- 最小限の消費リソース、Xilinx製MACコアの1/2

- 低価格、Xilinx製MACコアの1/5

2019/7/2

Design Gateway

# MAC機能とインターフェイス

- ・ 提供するMAC機能

- DesignGateway社IPコアで必要なMAC機能を実装

- FCS(CRC-32)計算

- 送信パケットへのPreamble,SFD,FCS挿入

- 受信パケットからのSFD検出と同期およびFCSチェック

- ・インターフェイス

- PHY側インターフェイスは64bit XGMII(156.25MHz)

- コントローラ側インターフェイスはAXI4-Stream

#### DG-10GEMAC-IPコアの特長1

- TOE10G-IPコア/UDP10G-IPコア専用MAC

- TOE10G-IP/UDP10G-IPコアと合わせてXilinx評価ボードで実機動作・検証する参照デザインを用意

- Xilinx製10GEMAC(EF-DI-25GEMAC)との互換性が高い (僅かな追加回路でXilinx製10GEMACとの交換が可能)

- DG製IPコアで必要な機能のみの実装で低価格を実現

2019/7/2 Design Gateway Page 5

## DG-10GEMAC-IPコアの特長2

- 超低レイテンシ

- DG製IPコアとの組み合わせに限定することで最適化

- 特に受信レイテンシがXilinx標準MACの半分以下

|                | 送信レイテンシ       | 受信レイテンシ         |

|----------------|---------------|-----------------|

| Xilinx製10GEMAC | 19.2ns (3clk) | 115.2ns (18clk) |

| DG-10GEMAC-IP  | 19.2ns (3clk) | 44.8ns (7clk)   |

10GEMACのレイテンシ比較 (clk freq.=156.25MHz)

#### DG-10GEMAC-IPコアの特長3

- 最小限の消費リソース

- DG製IPコアで使わないMAC機能は省略することでXilinx 製MACの約半分のリソース消費量

|                | CLB LUTs | CLB Registers | CLB |

|----------------|----------|---------------|-----|

| Xilinx製10GEMAC | 3498     | 3291          | 694 |

| DG-10GEMAC-IP  | 1873     | 1072          | 326 |

10GEMACの消費リソース比較 (Kintex-Ultrascale)

2019/7/2 Design Gateway Page 7

### DG-10GEMAC-IPコアの注意点

- DesignGateway社製10GbEコア専用

- 他社製のTCP/UDP向けIPコアとの接続はできません

- いくつかの制約事項あり

- ゼロ・パディングの挿入/抜去機能なし (ユーザ回路側で必要に応じて送信でのゼロ・パディング 追加や受信での余計なパディング無視が必要)

- 受信パケットの先頭バイトはバイトレーン0または4のみ (通常の使い方であれば特に問題にはなりません)

### 結論

- TOE10G-IP/UDP10G-IPコアとベストマッチ

- 最小のレイテンシ、消費リソース、そしてコスト

- 最大のパフォーマンス

- Xilinx標準MACコアと容易に交換可能 (Xilinx EMAC機能が必要になってもすぐ対応可能)

- Xilinx評価ボードで動作するプロジェクト

- 実パフォーマンスを確認可能

2019/7/2 Design Gateway Page 9

# D·G

### 問い合わせ

- ・ ホームページにデータシート等技術資料を用意

- TOE10G-IP: https://dgway.com/TOE10G-IP\_X.html

- UDP10G-IP: https://dgway.com/UDP10G-IP X.html

- ・ 問い合わせ

- 株式会社Design Gateway

- E-mail: info@dgway.com

# 改版履歴

| Rev. | 日時       | 履歴            |

|------|----------|---------------|

| 1.0J | 2019/7/2 | 日本語プレセン初版リリース |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

|      |          |               |

2019/7/2 Design Gateway Page 11