# PCIe クロスオーバー・アダプタ[AB16-PCIeXOVR]

# 取扱い説明書 [Ver2.0J]

#### はじめに

この度は PCIe クロスオーバー・アダプタ[型番: AB16-PCIeXOVR] (以下、アダプタと略します)をご採用頂き誠にありがとうございます。 本アダプタは、1/4/8-lane の PCIe (PCI-Express)に対応したホストーデバイス間の変換アダプタ基板で、PCIe インターフェイスを実装した Altera/Xilinx 製各評価ボードに適用できます。 アダプタ基板の部品面と半田面に 8-lane の PCIe ソケットを実装しており、それぞれホスト側/デバイス側として機能するよう送信信号と受信信号を lane ごとに直結しています。

FPGA 評価ボードに標準装備されるカード・エッジ型 PCIe コネクタはデバイス側で、例えばパソコンの PCIe ソケット に挿入し FPGA ボードをデバイス側として使います。 ところが FPGA ボードの PCIe コネクタを本アダプタのホスト側 PCIe ソケットと接続し、さらにデバイス側 PCIe ソケットに PCIe デバイスを接続することで、ホスト機能を実装した FPGA が本アダプタ経由で PCIe デバイスと通信できます。 このため、本アダプタは PCIe ホスト側機能を実装する FPGA アプリケーション開発に最適です。

また、DesignGateway 社製 NVMe-IP コアを評価する場合、本アダプタが必要となります。

#### 本アダプタの特長を以下に示します。

- ホスト側は PCI-Express 8-lane(4/1-lane ももちろん可)の FPGA 評価ボードと接続可能

- デバイス側も同じく 8/4/1-lane の PCIe デバイスと接続可能

- アダプタ上に PCIe 規格の低ジッタクロック発生源(デフォルト 100MHz の HSCL 差動信号)を実装

- PCIe クロックはホスト側とデバイス側の両方に同一クロック信号を供給

- ホスト~デバイス間の各サイドバンド信号はジャンパ・ソケットで切断/接続を個別に設定可能

- サイドバンド信号用ピンヘッダにユーザ独自のドータ基板向け 2.5V/3.3V の供給電源を出力

- リセットはホスト~デバイス直結とアダプタ基板上のリセット・スイッチをジャンパ・ソケットで選択可

- デバイス側にスイッチで ON/OFF 可能な 12V および 3.3V 電源を供給

- 冷却ファン用 12V 電源コネクタにより 12V ファンによる評価 SSD の強制冷却が可能

#### パッケージ内容

本アダプタのパッケージ内容は下記のとおりです。

● AB16-PCIeXOVR アダプタ: 1枚

## 基板外形

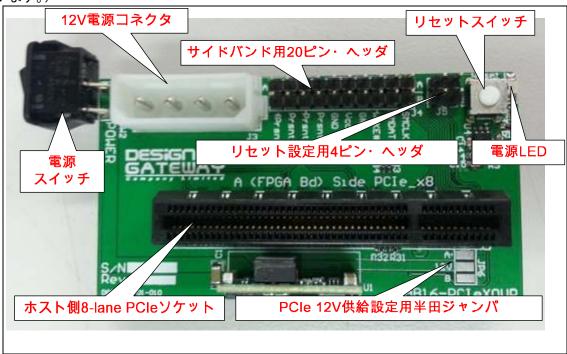

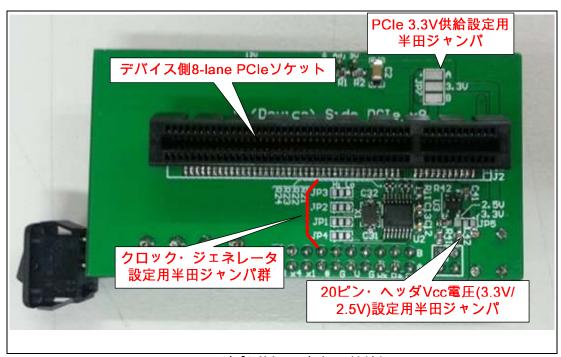

本アダプタの基板サイズは幅 40mm 長さ80mm です。 ホスト接続側およびデバイス接続側の基板外観写真をそれぞれ下図1および図2に示します。(注:基板改良により現行アダプタは電源コネクタ/電源スイッチの位置/向き等が変更されています。)

図 1: アダプタ基板のホスト接続側

図 2: アダプタ基板のデバイス接続側

#### ジャンパ説明

本アダプタは J4(20pin),J5(4pin),J6(3pin)の3種類のピンヘッダと JP1-JP7 の7種類の半田パターン・ジャンパがあり、ユーザによって設定が可能です。 各ジャンパおよびジャンパが関連する回路部分について以下に説明します。

## [1] J4 (20 ピンヘッダ)

J4 は下図 3 に示す 2 列×10 本の 20 ピンヘッダでホスト側/デバイス側それぞれの PCIe サイドバンド信号と接続します。また、3.3V または 2.5V で設定可能な Vcc 電源ピン(Pin#11/#12)も用意されているため、このピンヘッダを使ってユーザ独自のドータ基板を作成・接続しそこに電源を供給することも可能です。ピン番号は図 5 に示す定義で、基板端寄りの偶数ピンがホスト(A)側で奇数ピンがデバイス(B)側の信号です。

同じ列の偶数ピンと奇数ピン間を市販の 2.54mm ピッチのジャンパ・ソケットでショート接続することにより、ホスト側とデバイス側の同一信号同士を直結することができます。 J4 各ピンにおける具体的な接続については本ドキュメント末尾に添付した回路図を参照してください。

図 3: J4 ピンヘッダ (PCIe サイドバンド信号)

#### [2] J5 (5 ピンヘッダ)

J5 は下図 4 に示す 2 列×2 本の 4 ピンヘッダで、PCIe リセット信号を設定します。 ピン番号は図 6 に示す定義でジャンパ・ソケットの接続により以下のリセット設定が可能です。 アダプタ上にはリセット IC(U4)が実装されており、3.3V電源をモニタし検出電圧は 3.0V、リセット遅延時間は約 100msec です。 リセット IC は以下を使っています。

メーカ: T.I 型番: TPS3808G01DBV

また、リセットSW(SW1)により、ユーザが手動でリセット信号を発生することができます。

1-2 間ショート: ホスト側 PCIe リセット信号とデバイス側 PCIe リセット信号を直結

1-3 間ショート: アダプタ上リセット IC(U4)のリセット出力をデバイス側 PCIe リセット信号へ接続 2-4 間ショート: アダプタ上リセット IC(U4)のリセット出力をホスト側 PCIe リセット信号へ接続

図 4: J5 ピンヘッダ (PCIe リセット設定)

#### [3] J6 (3 ピンコネクタ)

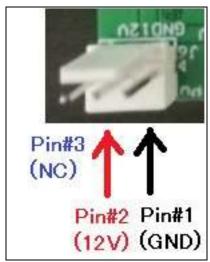

本アダプタには Fan 用コネクタが用意されています。 デバイス接続側に装着した SSD 等が発熱し強制冷却が必要な場合に冷却 FAN 用の電源として使えます。 下図 5 に示すように Pin#1-3 の順に(GND, 12V, 未接続)となります。

図 5: Fan 用コネクタ

#### [4] JP1-JP4 (半田パターン・ジャンパ)

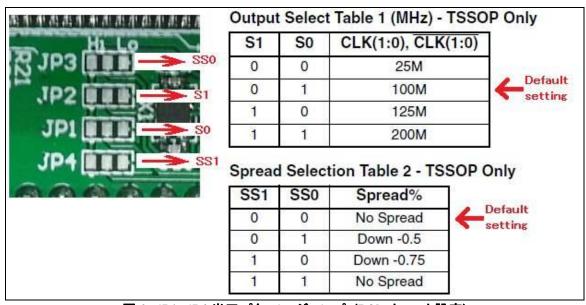

JP1~JP4 はアダプタ上に実装された PCIe クロック・ジェネレータのパラメータ設定用半田パターン・ジャンパで、設定について下図 6 に示します。 クロック・ジェネレータは以下のデバイスを使っています。

メーカ: IDT 型番:IDT5V41235PGG

JP1~JP4 は図各半田パターンの中央パッドがクロック・ジェネレータのそれぞれ S0,S1,SS0,SS1 ピンと接続しており、各パラメータを図 6 左側パッドの Hi(=1,Vcc)または右側パッドの Lo(=0,GND)と半田でショートすることにより設定します。 工場出荷時のデフォルトは JP1 のみ HiJP2-JP4 は Lo なので PCIe クロック周波数は 100MHz、SSC なしの設定です。

図 6: JP1-JP4 半田パターン・ジャンパ (PCIe クロック設定)

#### [5] JP5 (半田パターン・ジャンパ)

JP5 は J1 ピンヘッダのピン番号 11 および 12 にアサインされた外部向け Vcc 電源の電源電圧を設定するジャンパで図 7 に示します。 J1 ピンヘッダの上にユーザ独自のドータ基板等を作成、実装する場合にそのドータ基板に対して本ジャンパで設定した 2.5V あるいは 3.3V の電源を供給することができます。

図 7 の JP5 にて中央パッドが J1 ピンヘッダと接続しており、左側パッドとショートすると 2.5V が、右側パッドとショートすると 3.3V が選択されます。 工場出荷時は 3.3V が選択されています。

図 7: JP5 半田パターン・ジャンパ(Vcc 電源設定)

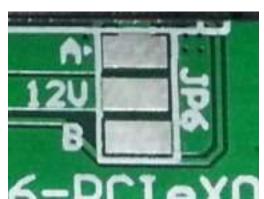

### [6] JP6 (半田パターン・ジャンパ)

下図8に示すJP6(部品面側に配置)にてホスト側PCIe およびデバイス側PCIe の12V電源の供給設定が可能です。図8にて中央パッドがアダプタの供給元12V電源で、上パッドと半田でショートすることによりホスト側PCIe に対して12Vを供給でき、下パッドと半田でショートするとデバイス側PCIe に対して12Vを供給できます。

工場出荷時のデフォルトではデバイス(B)側 PCIe のみ 12V が供給され、ホスト(A)側 PCIe には 12V は供給されません。

図 8: JP6 によるホスト側/デバイス側 PCIe の 12V 電源供給

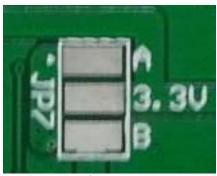

### [7] JP7 (半田パターン・ジャンパ)

下図9に示すJP7(半田面側に配置)にてホスト側PCIe およびデバイス側PCIeの3.3V電源の供給設定が可能です。図9にて中央パッドがアダプタの供給元3.3V電源で、上パッドと半田でショートすることによりホスト側PCIeに対して3.3Vを供給でき、下パッドと半田でショートするとデバイス側PCIeに対して3.3Vを供給できます。

工場出荷時のデフォルトではデバイス(B)側 PCIe のみ 3.3V が供給され、ホスト(A)側 PCIe には 3.3V は供給されません。

図 9: JP7 によるホスト側/デバイス側 PCIe の 3.3V 電源供給

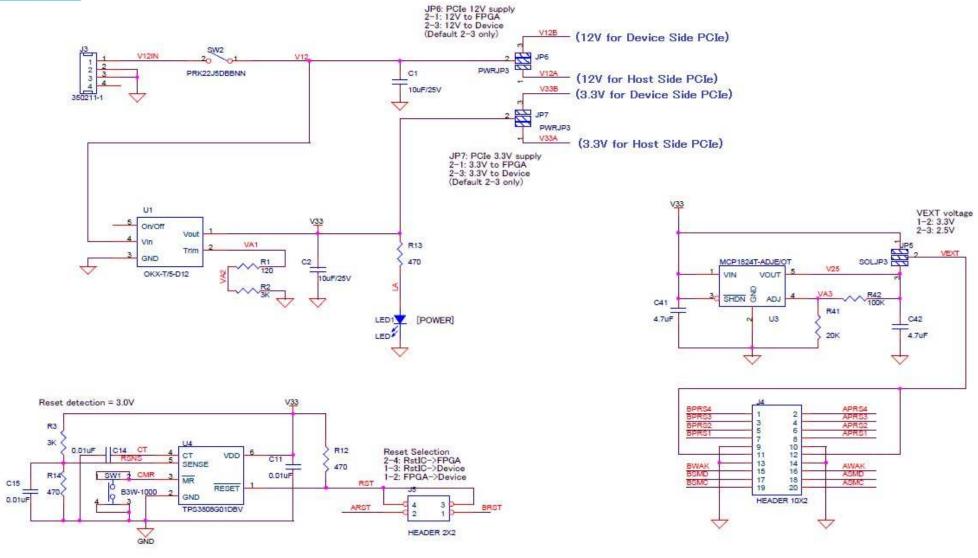

図 11: アダプタ回路図 (1/2)

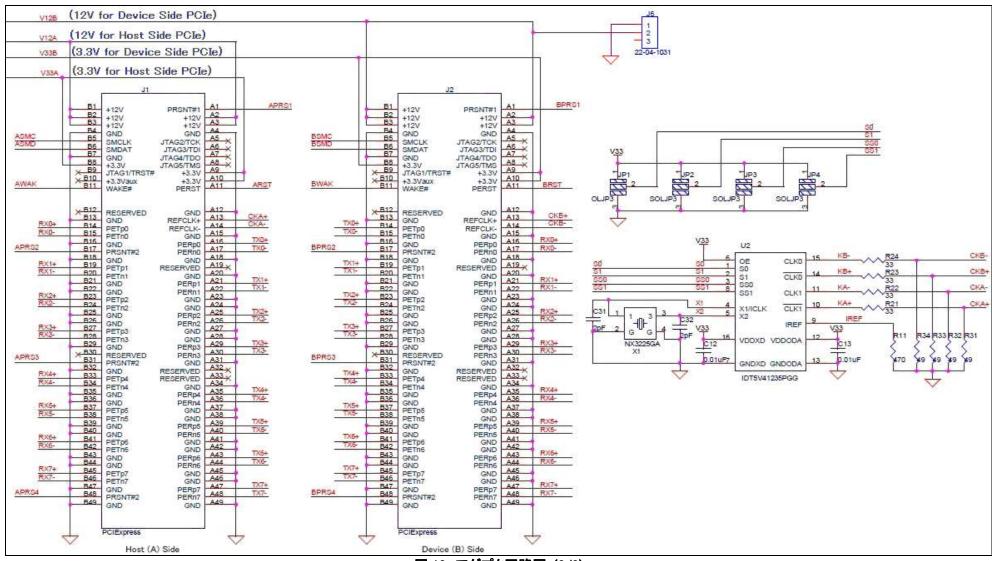

図 12: アダプタ回路図 (2/2)

# 免責事項

本アダプタを誤って使用することにより生じた FPGA 評価基板あるいは PCIe 接続デバイスの損傷については、その一切を免責事項とさせていただきます。 また、本アダプタはあくまで評価を目的としたものであり、FPGA 評価基板や接続先デバイスの PCIe 特性によっては正常に動作しない可能性がありますが、アダプタの製造不良以外は免責となります。

[問い合わせ先]

URL : <a href="http://www.dgway.com">http://www.dgway.com</a>

Email : <a href="mailto:info@dgway.com">info@dgway.com</a>

# 改版履歴

| リビジョン | 日付         | 内容                                           |

|-------|------------|----------------------------------------------|

| 0.1J  | 2015/09/15 | 日本語版の暫定発行(図3/図4写真なし)                         |

| 1.0J  | 2015/09/17 | 日本語版の初版発行                                    |

| 2.0J  | 2021/08/09 | 評価 SSD 冷却用 12V ファン電源コネクタ(J6)追加<br>付属アクセサリ類廃止 |