# NVMe IP Demo Instruction

Rev3.4 20-Apr-20

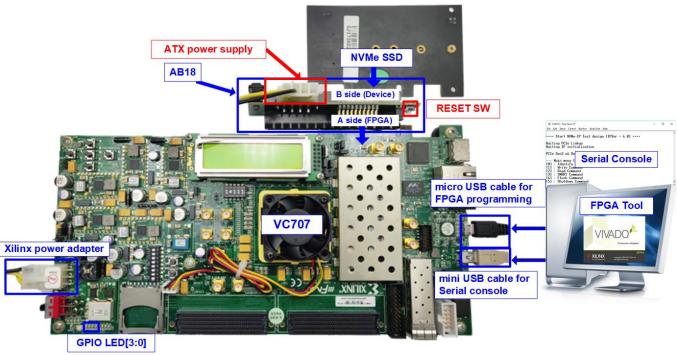

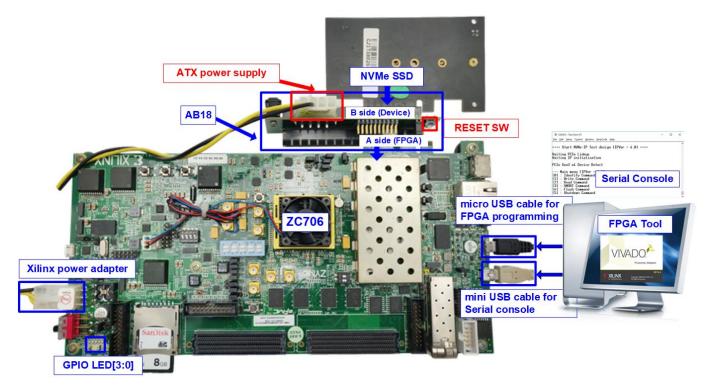

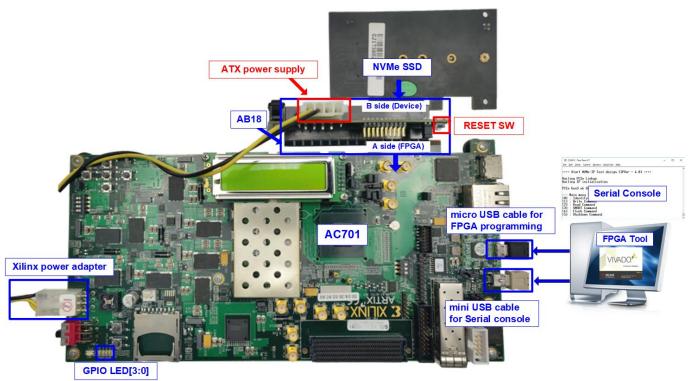

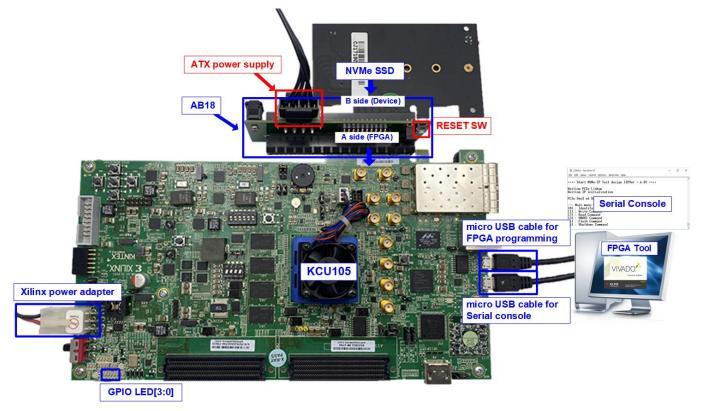

This document describes the instruction to run NVMe IP demo on FPGA development board by using the PCIe adapter board (AB18-PCIeX16/AB16-PCIeXOVR adapter board). The demo is designed to write/verify data with NVMe SSD. User controls the test operation through Serial console.

# 1 Environment Requirement

To run the demo on FPGA development board, please prepare following environment.

- 1) Supported FPGA Development board: ZC706, VC707, KCU105, ZCU106, and VCU118

- 2) PC installing Xilinx programmer software (Vivado) and Serial console software such as HyperTerminal and TeraTerm

- 3) The PCIe adapter board (AB18-PCIeX16/AB16-PCIeXOVR adapter board) provided by Design Gateway https://dgway.com/ABseries E.html

- 4) Xilinx power adapter for FPGA board

- 5) ATX power supply for PCIe adapter board

- 6) NVMe SSD connecting to B side (Device) of PCIe adapter board

- 7) One micro USB cable for programming FPGA, connecting between FPGA board and PC

- 8) One mini/micro USB cable for Serial console, connecting between FPGA board and PC

Figure 1-1 NVMe IP demo environment setup on VC707 (PCIe Gen2)

Figure 1-2 NVMe IP demo environment setup on ZC706 (PCIe Gen2)

Figure 1-3 NVMe IP demo environment setup on AC701 (PCIe Gen2)

Figure 1-4 NVMe IP demo environment setup on KCU105 (PCIe Gen3)

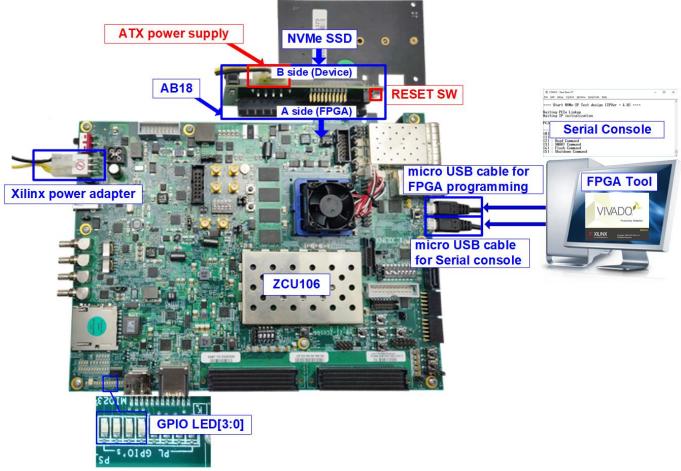

Figure 1-5 NVMe IP demo environment setup on ZCU106 (PCIe Gen3)

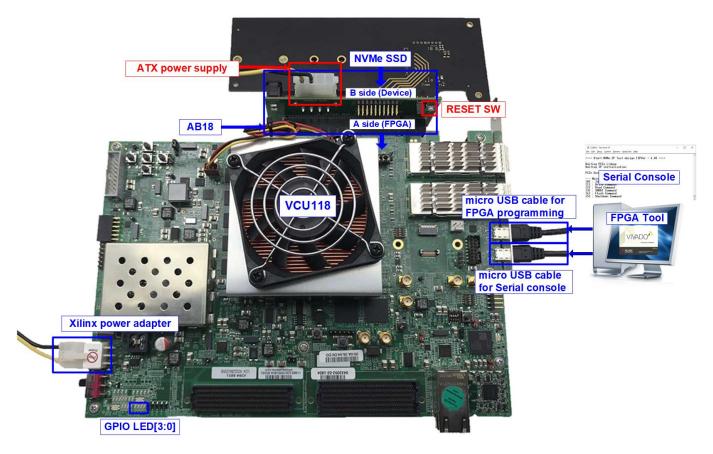

Figure 1-6 NVMe IP demo environment setup on VCU118 (PCIe Gen3)

## 2 Demo setup

- 1) Power off system.

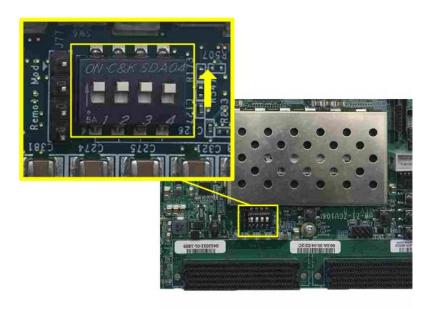

- 2) DIP Switch setting for JTAG configuration on Zynq board.

- a) For ZC706 board, set SW11="00000" to configure PS from JTAG and set SW4="01" to connect JTAG with USB-to-JTAG interface, as shown in Figure 2-1.

Figure 2-1 SW11 setting to configure PS from JTAG on ZC706

b) For ZCU106 board, set SW6=all ON to configure PS from JTAG, as shown in Figure 2-2.

Figure 2-2 SW6 setting to configure PS from JTAG on ZCU106

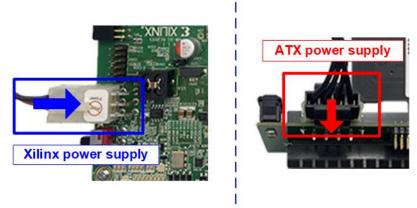

Connect ATX power supply to AB18-PCleX16 board and Xilinx power adapter to FPGA development board.

Figure 2-3 Power supply connection

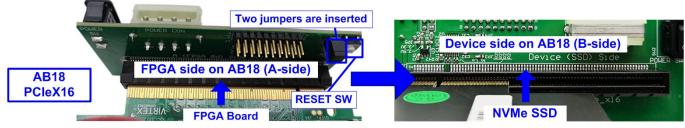

4) Confirm that two mini jumpers are inserted at J5 connector on AB18. After that, connect FPGA Side (A-side) on AB18 to PCIe connector on FPGA board and connect NVMe PCIe SSD to device side (B-Side) on AB18, as shown in Figure 2-4.

<u>Warning</u>: Please confirm that the SSD is inserted in the correct side of AB18 (B-side, not A-side) before power on system.

Figure 2-4 Connect Adapter board to NVMe SSD and FPGA board

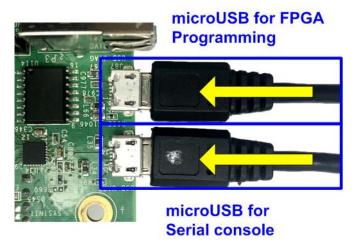

- 5) Connect USB cables for JTAG programming and Serial console.

- a) For AC701/VC707/ZC706, connect micro USB for JTAG and mini USB cable for Serial console.

- b) For KCU105/ZCU106/VCU118, connect two micro USB cables for JTAG and Serial console.

Figure 2-5 USB cable connection

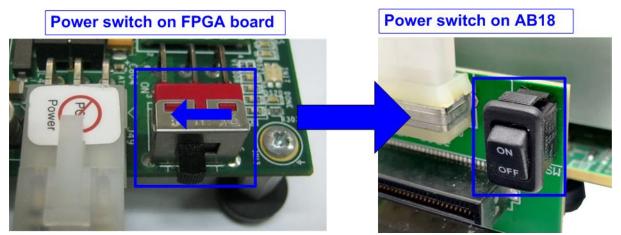

6) Power on FPGA development board, ATX power supply, and AB18, as shown in Figure 2-6.

Figure 2-6 Turn on power switch on FPGA and adapter board

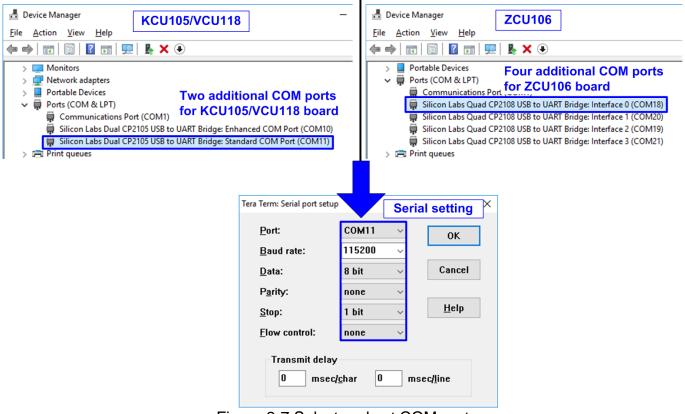

7) On PC, additional COM port is detected after connecting USB cables to FPGA board. On Ultrascale/Ultrascale+ board, there are more than one COM ports detected.

In case of KCU105 and VCU118, select Standard COM port. In case of ZCU106, select the lowest number for ZCU106 board, as shown in Figure 2-7.

On Serial console, the setting is as follows. Buad rate=115,200, Data=8-bit, Non-Parity, and Stop = 1.

Figure 2-7 Select and set COM port

- 8) Download and program configuration file and firmware to FPGA board.

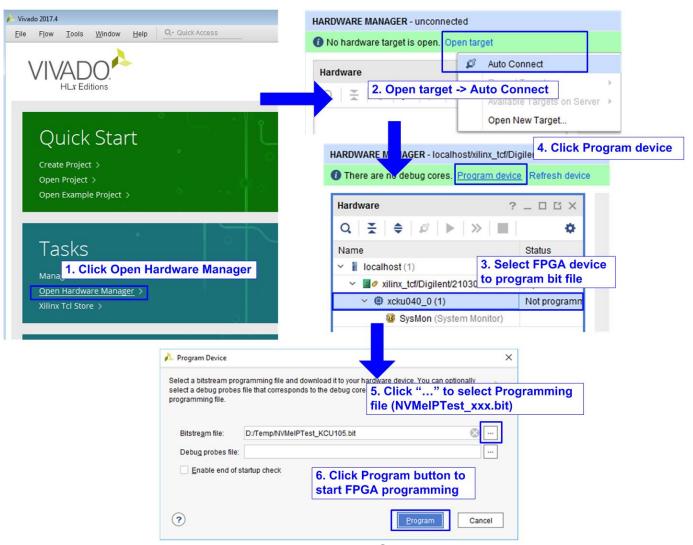

- a) For AC701/VC707/KCU105/VCU118, configure FPGA by using Vivado, as shown in Figure 2-8.

Figure 2-8 Program FPGA by Vivado

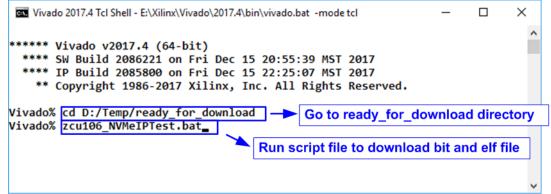

b) For ZC706/ZCU106 board, open Vivado TCL shell and change directory to ready\_for\_download or directory that batch file is located. Next, type zc706\_NVMeIPTest.bat or zcu106\_NVMeIPTest.bat, as shown in Figure 2-9.

Figure 2-9 Command script to download demo file on Vivado TCL shell

9) Check LED status on FPGA board. The description of LED is as follows.

Table 2-1 LED Definition

| GPIO LED | ON                     | OFF                                            |

|----------|------------------------|------------------------------------------------|

| 0        | Normal operation       | Clock is not locked or reset button is pressed |

| 1/R      | System is busy         | Idle status                                    |

| 2/C      | IP Error detect        | Normal operation                               |

| 3/L      | Data verification fail | Normal operation                               |

10)After programming completely, LED[0] and LED[1] are ON during PCle initialization process. Then, LED[1] changes to OFF after PCle completes initialization process.

## **ZCU106**

## AC701/VC707/KCU105/VCU118

Figure 2-10 LED status after program configuration file and PCIe initialization complete

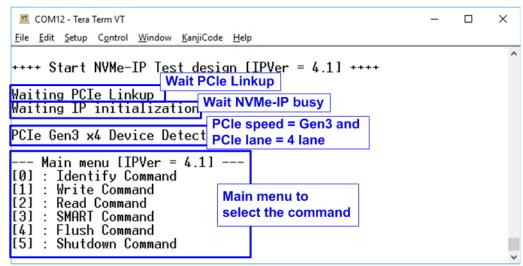

11)On the console, the message is displayed to show current status as follows.

"Waiting PCIe Linkup" is displayed after finishing configuration.

After PCle is linkup, "Waiting IP initialization" is displayed.

After finishing NVMe IP initialization, PCIe speed and number of PCIe lanes are displayed. Finally, main menu to run six commands is shown on the console.

Figure 2-11 Main menu after IP finishes initialization

#### 3 Test Menu

## 3.1 Identify Command

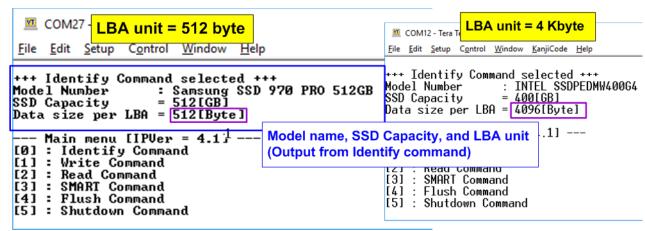

Select '0' to send Identify command to NVMe SSD.

Figure 3-1 Test result when running Identify command

After finishing the operation, the SSD information output from Identify command is displayed. The console shows three values.

- 1) SSD model number: This value is decoded from Identify controller data.

- 2) SSD capacity: This value is signal output from NVMe-IP.

- 3) Data size per LBA: This value is signal output from NVMe-IP. Two values are supported, i.e. 512 byte and 4 Kbyte.

#### 3.2 Write Command

Select '1' to send Write command to NVMe SSD.

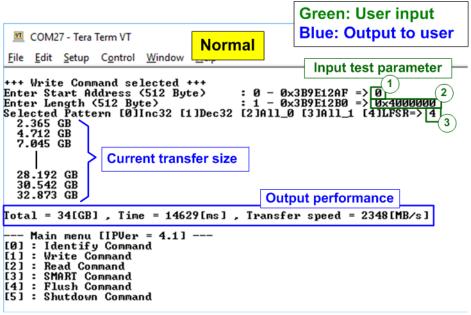

Figure 3-2 Test result when running Write command

User inputs three parameters as follows.

- 1) Start Address: Input start address to write SSD as 512-byte unit. The input is decimal unit when user enters only digit number. User can add "0x" to be prefix for hexadecimal unit. When LBA unit of SSD is 4 Kbyte, this input must be aligned to 8.

- 2) Transfer Length: Input total transfer size as 512-byte unit. The input is decimal unit when user enters only digit number. User can add "0x" to be prefix for hexadecimal unit. When LBA unit of SSD is 4 Kbyte, this input must be aligned to 8.

- 3) Test pattern: Select test data pattern for writing to SSD. There are five patterns, i.e. 32-bit incremental, 32-bit decremental, all-0, all-1, and 32-bit LFSR counter.

When all inputs are valid, the operation begins. During writing data, current transfer size is displayed on the console every second to show that system is still alive. Finally, total size, total time usage, and test speed are displayed on the console to be a test result.

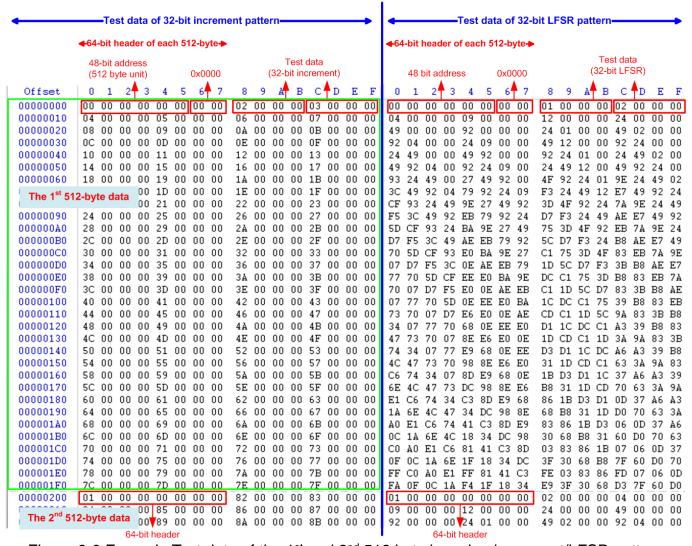

Figure 3-3 Example Test data of the 1st and 2nd 512 byte by using increment/LFSR pattern

Test data in SSD is split into 512-byte unit. For incremental, decremental, or LFSR pattern, each 512-byte data has unique 64-bit header consisting of 48-bit address (in 512-byte unit) and 16-bit zero value. The data after 64-bit header is the test pattern which is selected by user.

The left window of Figure 3-3 shows the example when using 32-bit incremental pattern while the right window shows the example when using 32 bit LFSR pattern. The unique header is not included when running all-0 or all-1 pattern.

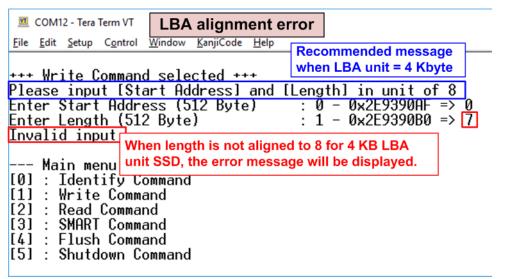

When user runs Write or Read command with 4-Kbyte LBA SSD, there is the message displaying on the console to show the input limitation which must be aligned to 8, as shown in Figure 3-4. When the input does not align to 8, "Invalid input" is displayed and the operation is cancelled.

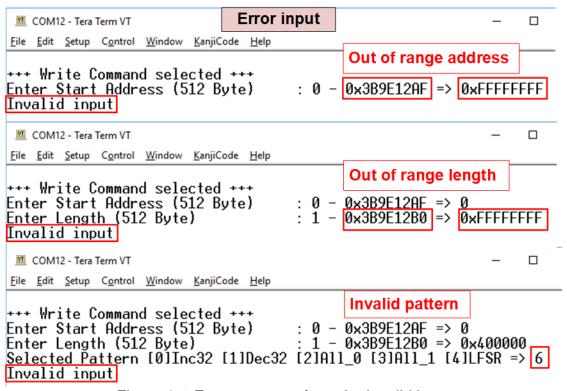

Also, Figure 3-5 shows the example when the input is out of the recommended range for each parameter. The console displays "Invalid input" and then the operation is cancelled.

Figure 3-4 Error message when the input is unaligned for SSD with 4KB LBA unit

Figure 3-5 Error message from the invalid input

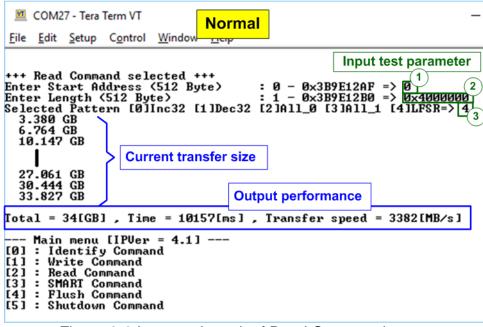

#### 3.3 Read Command

Select '2' to send Read command to NVMe SSD.

Figure 3-6 Input and result of Read Command menu

User inputs three parameters as follows.

- 1) Start Address: Input start address to read SSD as 512-byte unit. The input is decimal unit when user enters only digit number. User can add "0x" to be prefix for hexadecimal unit. When LBA unit of SSD is 4 Kbyte, this input must be aligned to 8.

- 2) Transfer Length: Input total transfer size as 512-byte unit. The input is decimal unit when user enters only digit number. User can add "0x" to be prefix for hexadecimal unit. If LBA unit of SSD is 4 Kbyte, this input must be aligned to 8.

- 3) Test pattern: Select test data pattern to verify data from SSD. Test pattern must be matched with the pattern using in Write Command menu. There are five patterns, i.e. 32-bit incremental, 32-bit decremental, all-0, al-1, and 32-bit LFSR counter

Similar to Write command menu, test system reads data from SSD when all inputs are valid. During reading data, current transfer size is displayed on the console every second to show that system is still alive. Total size, total time usage, and test speed are displayed after finishing the operation.

"Invalid input" is displayed when some inputs are invalid or unaligned to 8 (when connecting to 4-KB LBA SSD).

Figure 3-7 shows error message when data verification is failed. "Verify fail" is displayed with the information of the 1<sup>st</sup> failure data, i.e. the error byte address, the expected value, and the read value.

User can press any key(s) to cancel read operation or wait until finishing Read command. Similar to the normal condition, the output performance is displayed on the console when the user does not enter any key(s) to stop the operation.

When cancelling the operation, the read command still runs as the background process. It is recommended to power-off/on AB18, and then press "RESET" button to restart system.

Figure 3-7 Data verification is failed

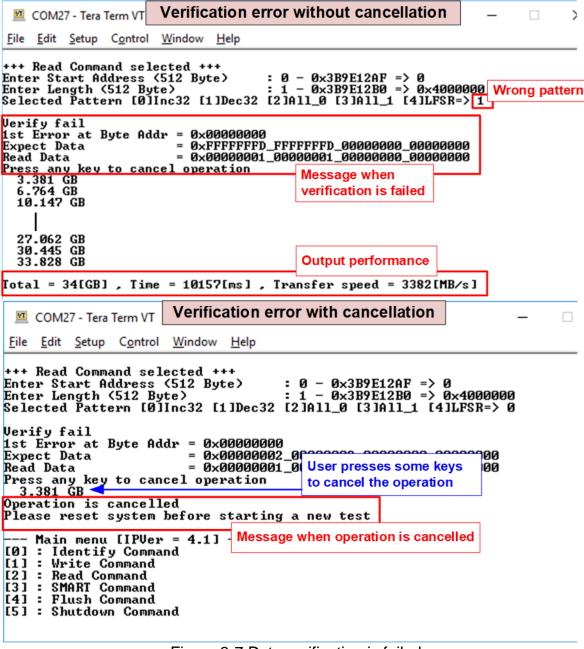

#### 3.4 SMART Command

Select '3' to send SMART command to NVMe SSD.

Figure 3-8 Test result when running SMART command

When finishing the operation, SMART/Health Information (output from SMART command) is displayed as shown in Figure 3-8. The console shows six parameters, described as follows.

- 1) Temperature in °C unit.

- 2) Total Data Read decoded as GB/TB unit. Additionally, raw data without decoding is displayed in 128-bit hexadecimal unit. The unit size of raw data is 512,000 byte.

- 3) Total Data Written decoded as GB/TB unit. Additionally, raw data without decoding is displayed in 128-bit hexadecimal unit. The unit size of raw data is 512,000 byte.

- 4) Power On Cycles: Display the number of power cycles.

- 5) Power On Hours: Display period of time in hours to show how long the SSD has been powered on.

- 6) Unsafe Shutdowns: Display the number of unsafe shutdowns of SSD

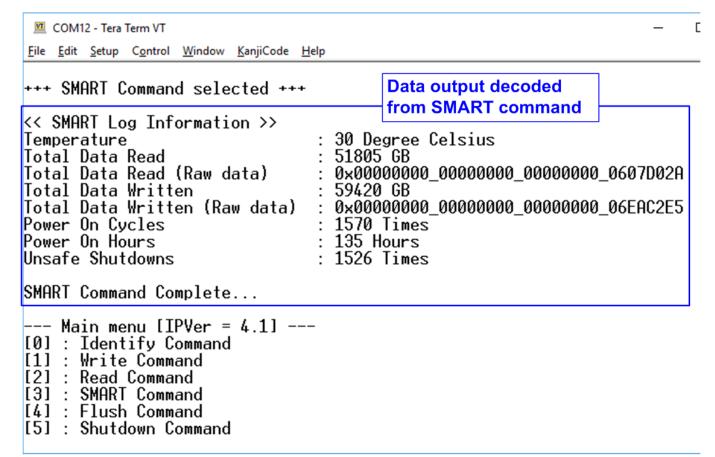

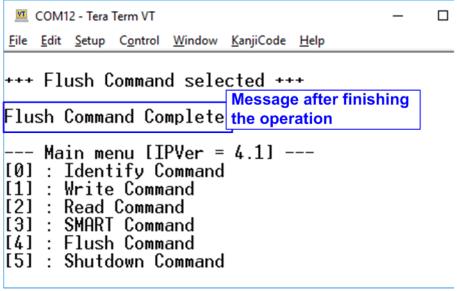

#### 3.5 Flush Command

Select '4' to send Flush command to NVMe SSD.

Figure 3-9 Test result when running Flush command

"Flush Command Complete" is displayed after finishing Flush operation.

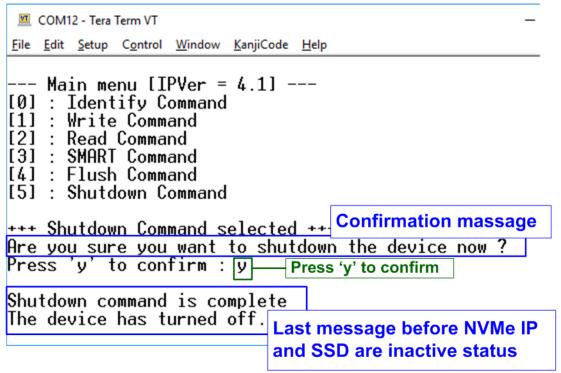

#### 3.6 Shutdown Command

Select '5' to send Shutdown command to NVMe SSD.

Figure 3-10 Shutdown Command with confirmation

The confirmation message is displayed on the console. User inputs 'y' or 'Y' to confirm the operation or inputs other keys to cancel the operation.

After finishing Shutdown operation, "Shutdown command is complete" is displayed on the console as the last message. Main menu is not displayed anymore. User needs to power off/on test system to start new test operation.

# 4 Revision History

| Revision | Date      | Description                                    |

|----------|-----------|------------------------------------------------|

| 1.0      | 2-Jun-16  | Initial version release                        |

| 1.1      | 17-Jun-16 | Support KCU105 board                           |

| 1.2      | 5-Sep-16  | Support ZC706 board                            |

| 1.3      | 9-Sep-16  | Support KC705 board                            |

| 1.4      | 29-Sep-16 | Support Zynq Mini-ITX board                    |

| 1.5      | 28-Oct-16 | Support VC709 board                            |

| 1.6      | 14-Dec-16 | Update performance result of new buffer system |

| 2.0      | 8-Jun-17  | New NVMe IP version                            |

| 2.1      | 27-Jul-17 | Add LFSR pattern                               |

| 2.2      | 30-Nov-17 | Support ZCU106 board                           |

| 2.3      | 13-Mar-18 | Add numbers of lane message                    |

| 3.0      | 19-Jul-18 | Support Shutdown, SMART, and Flush command     |

| 3.1      | 23-Nov-18 | Support AC701 board                            |

| 3.2      | 3-May-19  | Support VCU118 board                           |

| 3.3      | 28-Jan-20 | Update board demo by using AB18                |

| 3.4      | 20-Apr-20 | Remove power adapter cable from AB18           |