FPGA devices are highly versatile, allowing for seamless adaptation to evolving standards, making them a crucial choice for mission-critical applications like Aerospace. They boast high reliability and radiation hardening features, ensuring optimal performance even in challenging environments.

In the realm of Aerospace, the need for efficient Data Storage, Networking, and Security solutions is paramount. FPGA-based Design Gateway IP cores address these needs, offering a strategic advantage. These cores optimize performance, energy usage, and resource allocation, making them ideal for high-performance applications in Aerospace.

Unleash Real-Time Aerospace Data Processing

Blazing-Fast FPGA Solution Records & Processes Space & Defense Data Instantly

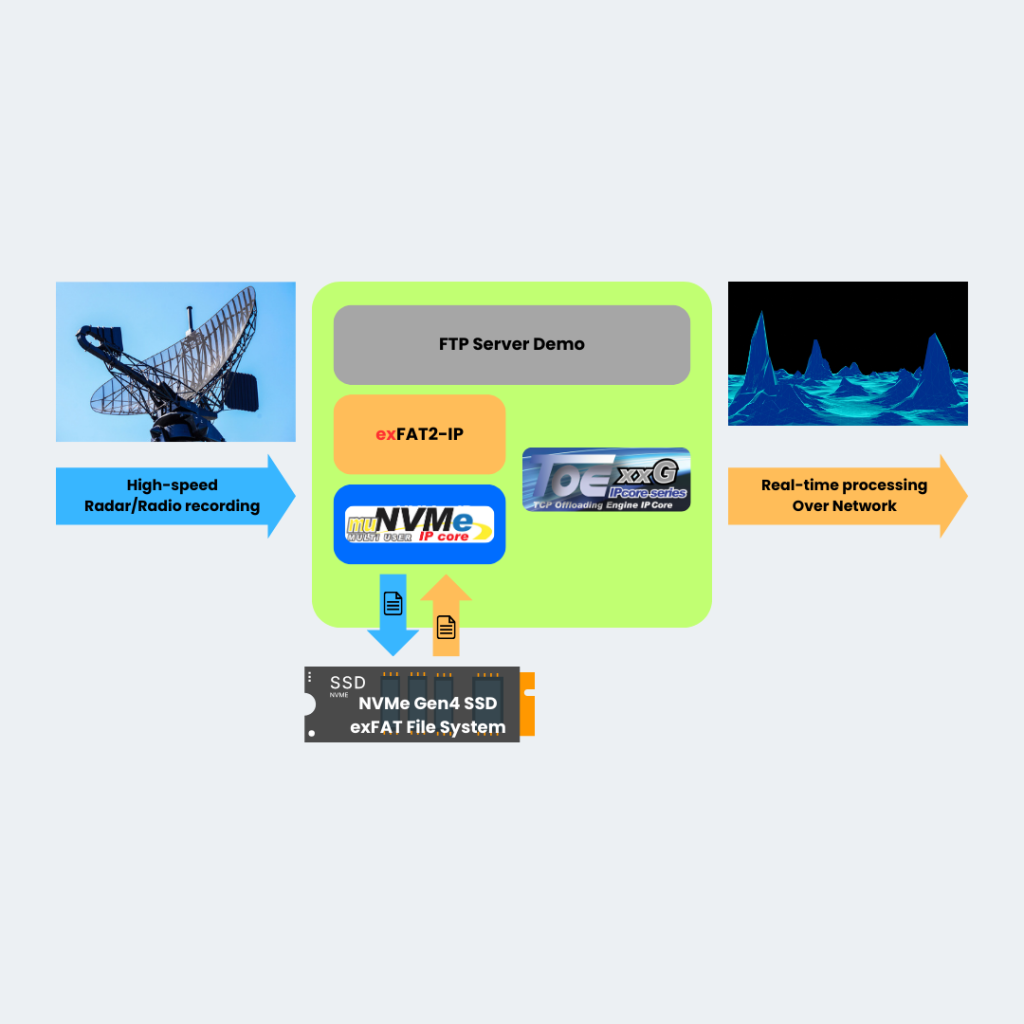

Revolutionize aerospace data processing workflows with our breakthrough FPGA-based solution! This innovative reference design empowers you to capture and process massive aerospace data (10GB/s+) in real time, eliminating CPU and OS bottlenecks. Simultaneously, read recorded data over the network for instantaneous diagnosis, all within a simplified system.

No longer struggle with CPU limitations: Our IP solutions leverage powerful FPGAs for high-speed recording and processing, bypassing the traditional CPU and OS overhead.

Key Advantages

- Real-time & high-speed NVMe SSD recording: Capture massive aerospace data instantly at 10GB/s+ rates.

- Simultaneous exFAT file reading over network: Streamline workflows by accessing recorded data instantly for real-time analysis.

- Simplify system with NO CPU & OS required: Reduce complexity and cost by eliminating CPU and OS dependencies.

- Available reference design: Accelerate your development with a pre-built reference design, saving time and resources.

- Unleash FPGA potential: Unlock the full power of FPGAs for custom aerospace data processing and analysis algorithms.

Empower light-speed data recording, and faster analytics, and revolutionize real-time aerospace data processing with this cutting-edge FPGA solution.

Industrial Applications use cases for AES-GCM 100G IP Core

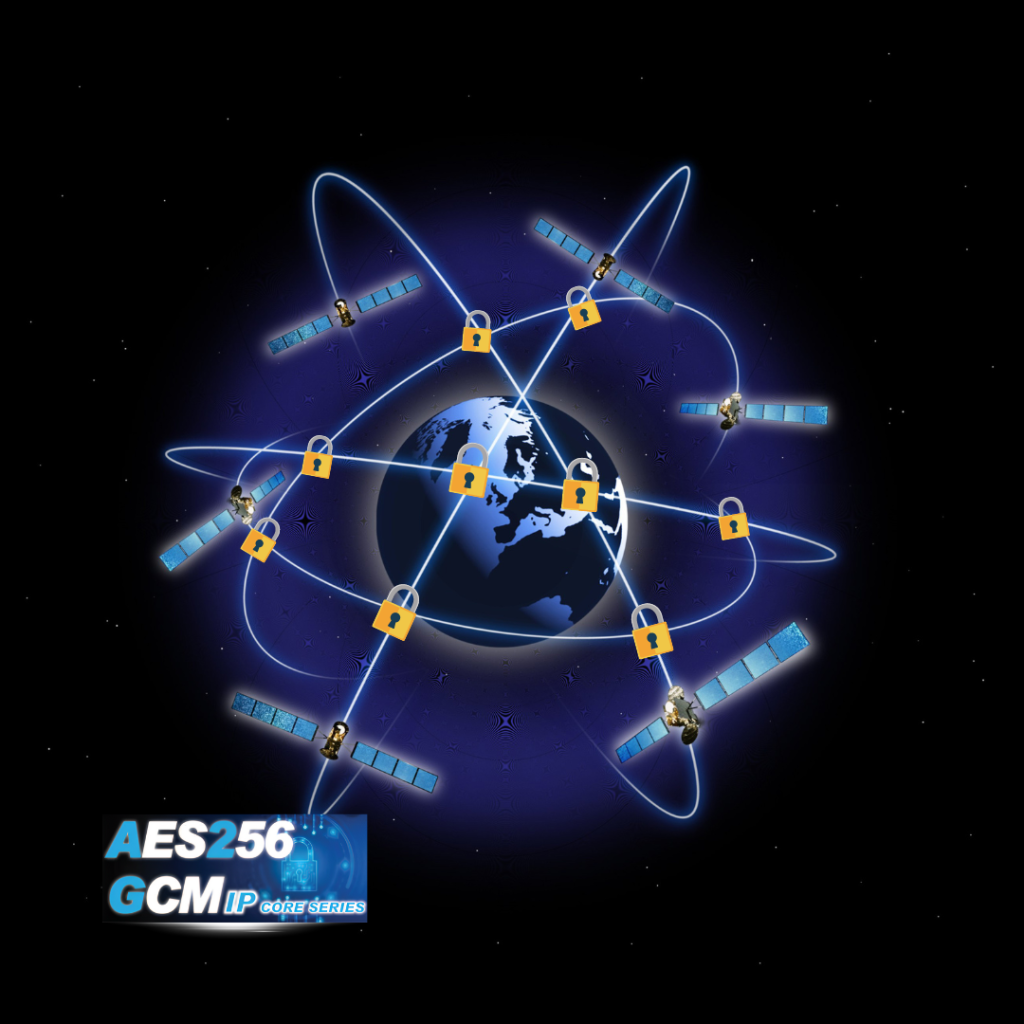

In satellite communication, data security is paramount. The AES-GCM IP Core on FPGA can be implemented to encrypt data before it is transmitted to the satellite constellation network or the ground station.

High bandwidth & secure space-to-ground communication

Map/Terrain/Weather satellites gather atmospheric information and secure it with AES-GCM encryption prior to transmission. The receiving ground station, outfitted with an FPGA that employs AES-GCM, deciphers the data in real-time at a throughput of 100~200 Gbps. This guarantees the secrecy and integrity of the conveyed data, thwarting unauthorized intrusion and alteration.

Satellite mesh constellation network

Communication/Internet satellites necessitate high-bandwidth and low-latency communication throughout a mesh constellation network. Each intercommunication link can attain speeds of 100Gbps or more by utilizing AES-GCM on FPGA. This ensures confidentiality, data integrity, and protection against side-channel attacks, all while maintaining high-speed communication.

Examples of DG’s IP Core Applications

Space

exploration system

Satellite

tracking station

Base

station system

Radar

system

Marine

sonar

Success Stories & Application Example

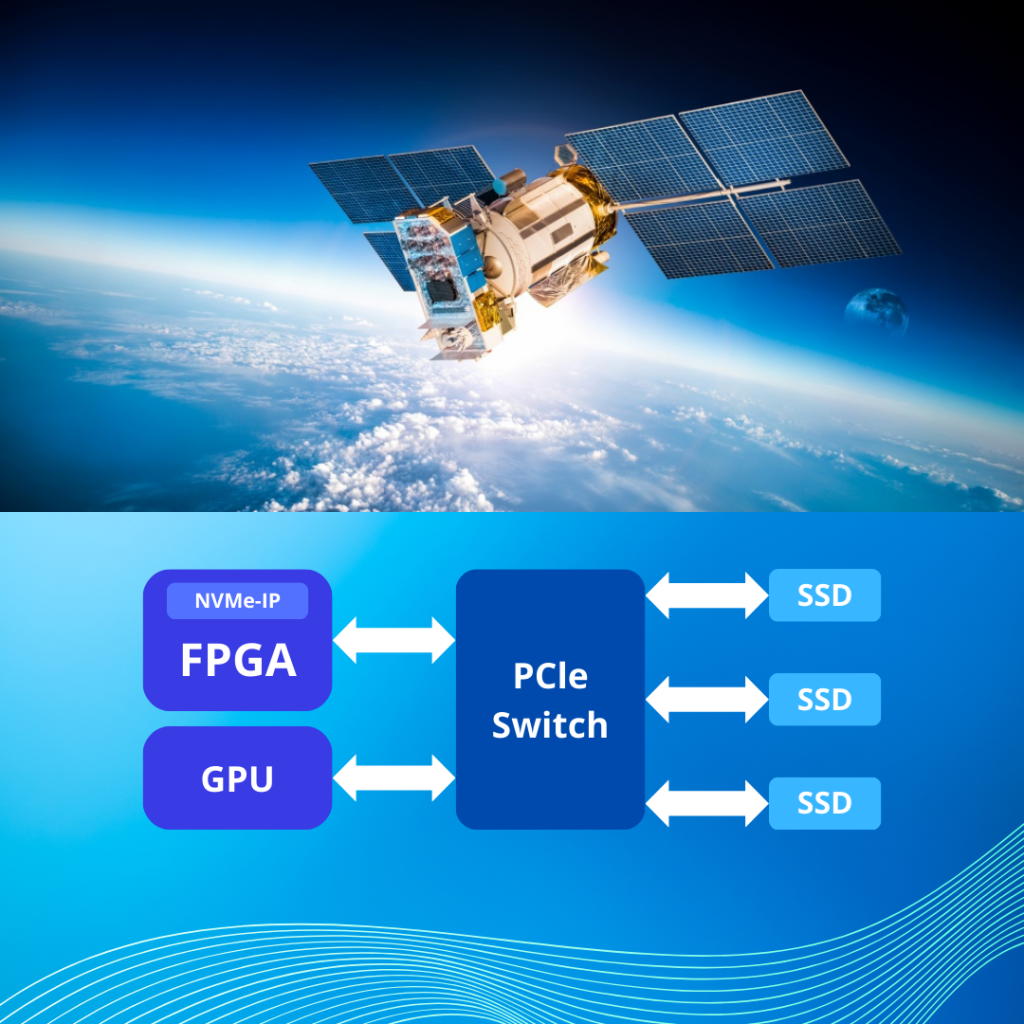

Key Factors

- NVMe with PCIe Gen3 soft IP (NVMeG3-IP) to support FPGA which does not have PCIe hard IP

- PCIe switch option to support connecting both FPGA and GPU

- Reference design to shorten development time

Key Factors

- NVMe with PCIe Gen3 soft IP (NVMeG3-IP) to support FPGA which does not have PCIe hard IP

- PCIe switch option to support connecting both FPGA and GPU

- Reference design to shorten development time