デザイン・ゲートウェイ Hot!ニュース

2023年7月号(2)

|

ウェブで開く デザイン・ゲートウェイ Hot!ニュース 2023年7月号(2) |

FPGA アクセラレーター・システム | ターンキー・システム・ソリューション |

|

詳しくはこちら | 購入する |

| デザイン・ゲートウェイは、AMD Xilinx VARパートナーとして、FPGAアクセラレーター・カードを提供しております。またFPGAアクセラレーター・カード搭載ターンキー・システムと各種IPコア リファレンス・デザインおよびデモを準備、評価&開発をシームレスに行う環境を提供致します。

|

|

超低遅延ネットワークIPについて詳しくはこちら |

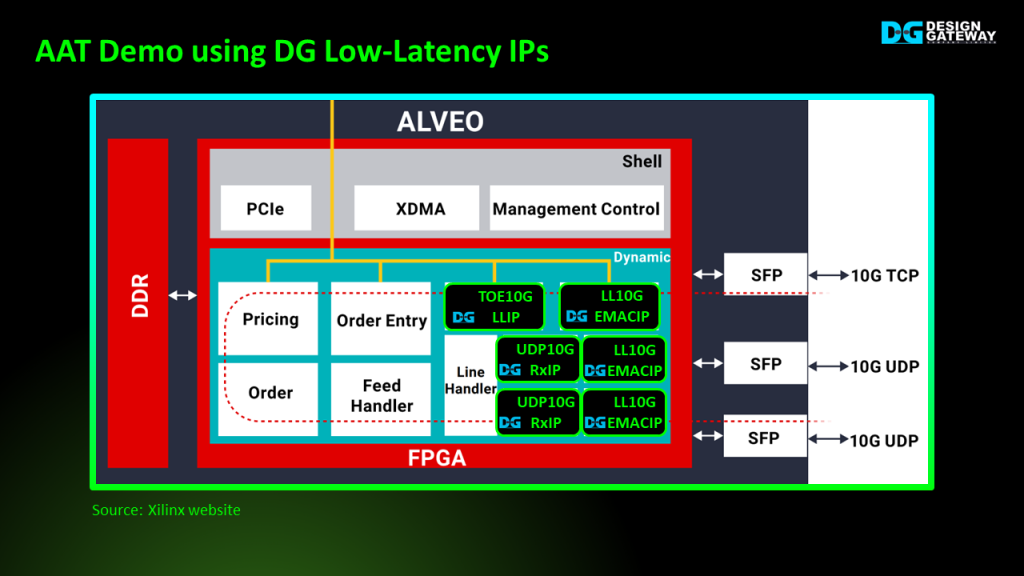

超低遅延ネットワークIP使用 AATデモ

AAT(Accelerated Algorithmic Trading) は、HLSを使用して設計された様々なハードウェア・ブロックから構成され、ユーザが必要に応じてアルゴリズムを変更し、市場データや取引戦略を処理することができます。超低レイテンシーを達成するため、Xilinx標準デザインに当社の低レイテンシー・ネットワークIPコアEMAC用LL10GEMAC-IP、UDPパケット受信用UDP10GRx-IP、低遅延TCP/IPパケット送信用TOE10GLL-IPを統合しました。 |

| ブログ記事: | |

|

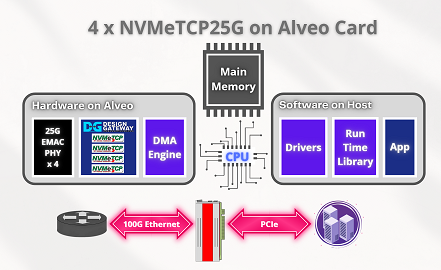

4 x NVMeTCP25G IP デモ

4 x NVMeTCP25Gリファレンス・デザインは、Alveo FPGAカードの100GbE(25Gx4)イーサネット・インターフェース・ポートをフルに活用し、NVMeTCPターゲットとAlveoのNVMe/TCPホスト性能を実証します。 各NVMeTCP接続性能は、NVMeTCPターゲットに依存しますが2GB/s超を達成します。 NVMeTCP25G IPについて詳しくはこちら |

| ブログ記事: | |

TOE100G IPについて詳しくはこちら |

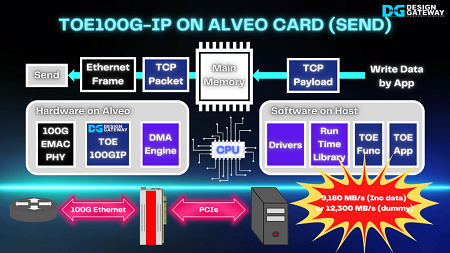

完全ハードウェア 100G TCPオフロード

100Gビット速度でのTCP伝送はCPUにとって大きな負荷となり、ハードウェア・アクセラレーターなしで持続的に高スループットを達成することは困難です。 TOE100G-IPコアは、純ハードウェア・ロジックにより、TCP伝送をCPUから完全にオフロードするように設計されています。Alveoカード上のデモ・アプリケーションでは、最小限のCPU使用量でほぼ100Gビットのスループットを達成します。 |

| ブログ記事: | |

| アプリケーション事例 |

| FPGAとデザイン・ゲートウェイのIPコアを利用することで実現するアプリケーション事例が DG's IP core Solutions FOR VERTICAL MARKET ページにて紹介されています。 詳細はこちら | ||||||||

航空宇宙 |

自動車 |

放送 |

教育 |

エンタメ |

金融 |

製造 |

医療 |

計測 |

| 株式会社デザイン・ゲートウェイ | 会社概要 | 個人情報保護 | 配信停止 | お問い合わせ | (c) 2023 Design Gateway Co., Ltd. |